# **Application Note: SY8284B**

## High Efficiency Fast Response, 4A, 23V Input **Synchronous Step Down Regulator**

## **General Description**

The SY8284B develops a high efficiency synchronous step-down DC/DC regulator capable of delivering 4A current. The device integrates main switch and synchronous switch with very low R<sub>DS(ON)</sub> to minimize the conduction loss. In addition, it operates at pseudoconstant frequency of 600kHz under heavy load conditions to minimize the size of inductor and capacitor. SY8284B also provides a fixed 3.3V LDO with 100mA current capability, which can be used for powering the external peripheries, such as the keyboard controller in notebook. The 3.3V LDO can switch over to Buck regulator output to save power loss.

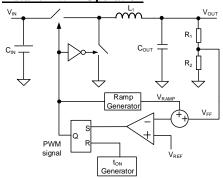

Silergy's proprietary Instant-PWM<sup>TM</sup> fast-response, constant-on-time (COT) PWM control method supports high input/output voltage ratios (low duty cycles), and fast transient response while maintaining a near constant operating frequency over line, load and output voltage ranges. This control method provides stable operation without complex compensation and even with low ESR ceramic capacitors.

The SY8284B operates over a wide input voltage range from 4V to 23V. Cycle-by-cycle current limit, input under voltage lock-out, internal soft-start, output under voltage protection and over voltage protection, and thermal shutdown provide safe operation in all operating conditions.

## **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY8284BRAC      | QFN3×3-20    |      |

### **Features**

- Low R<sub>DS(ON)</sub> for Internal Switches (top/bottom):  $85/35 \text{ m}\Omega$

- Wide Input Voltage Range: 4~23V

- Integrated Bypass Switch:  $1.5\Omega$

- Instant PWM Architecture to Achieve Fast Transient Responses

- Internal 1.2ms Soft-start Limits the Inrush Current

- Pseudo-constant Frequency: 600kHz

- Fixed 3.338V Output Voltage

- 4A Output Current Capability

- 100mA LDO Current Capability

- ±1% Internal Reference Voltage

- Power Good Indicator

- **Output Discharge Function**

- **Output Current Limit Protection**

- Latch-off Mode Output Under Voltage Protection

- Latch-off Mode Output Over Voltage Protection

- Latch-off Mode Over Temperature Protection

- Input Under Voltage Lock-out(UVLO)

- RoHS Compliant and Halogen Free

- Compact package: OFN3×3-20

## **Applications**

- LCD-TV/Net-TV/3DTV

- Set Top Box

- Notebook

- High Power AP

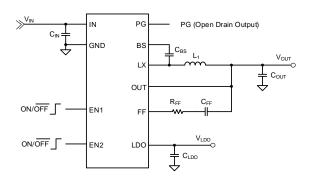

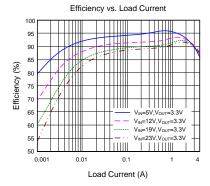

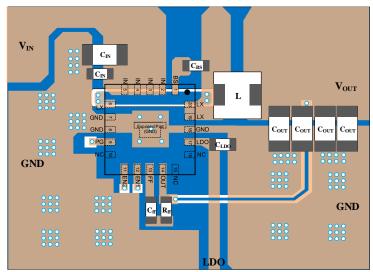

## **Typical Applications**

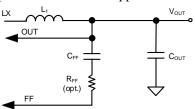

Figure 1. Schematic Diagram

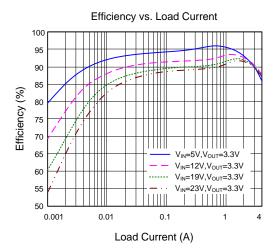

Figure 2. Buck Efficiency vs. Load Current

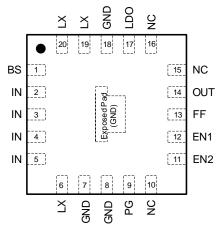

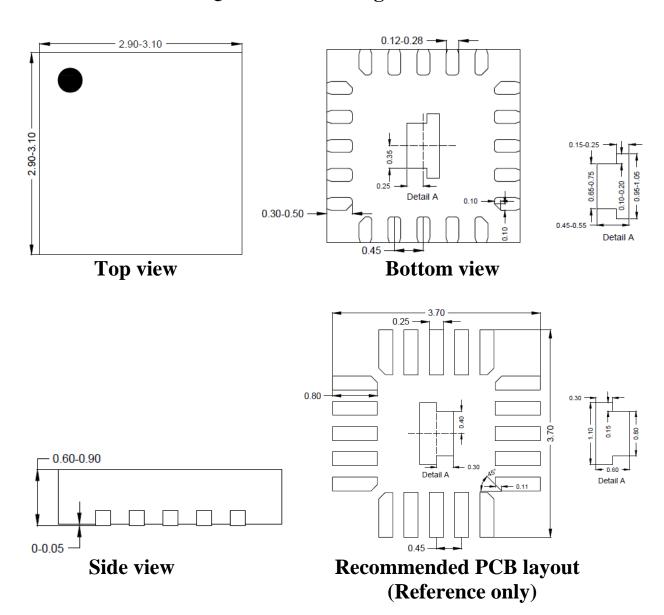

# Pinout (top view)

(QFN3×3-20)

Top Mark: BIE xyz, (Device code: BIE, x=year code, y=week code, z= lot number code)

| Pin Name | Pin Number   | Pin Description                                                                     |  |  |

|----------|--------------|-------------------------------------------------------------------------------------|--|--|

| BS       | 1            | Boot-strap pin. Supply high side gate driver. Connect a 0.1 µF ceramic capacitor    |  |  |

| ъъ       | 1            | between the BS pin and the LX pin.                                                  |  |  |

| IN       | 2, 3, 4, 5   | Input pin. Decouple this pin to GND pin with at least a10 µF ceramic capacitor.     |  |  |

| LX       | 6, 19, 20    | Inductor pin. Connect this pin to the switching node of the inductor.               |  |  |

| GND      | 7, 8, 18, EP | Ground pin.                                                                         |  |  |

| PG       | 9            | Power good Indicator. Open drain output when the output voltage is within 90%       |  |  |

| PG       |              | to 120% of regulation point.                                                        |  |  |

| NC       | 10, 15, 16   | Not connected.                                                                      |  |  |

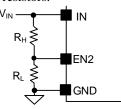

| EN2      | 11           | Enable control of the IC and internal LDO. Pull this pin high to turn on the IC and |  |  |

| ENZ      |              | internal LDO. Do not leave this pin floating.                                       |  |  |

| EN1      | 12           | Enable control of the DC/DC regulator. Pull this pin high to turn on the regulator. |  |  |

| ENI      | 12           | Do not leave this pin floating.                                                     |  |  |

| FF       | 13           | Output feed forward pin. Connect RC network from the output to this pin.            |  |  |

| OUT      | 14           | Output pin. Connect to the output of DC/DC regulator. The pin also provides the     |  |  |

| 001      |              | bypass input for internal LDO.                                                      |  |  |

| LDO      | 17           | 3.3V LDO output. Decouple this pin to ground with at least a 4.7 µF capacitor.      |  |  |

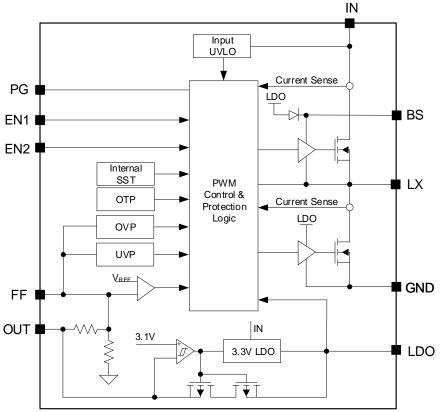

# **Block Diagram**

Figure 3. Block Diagram

# Absolute Maximum Ratings (Note 1)

| IN Voltage                                                                       | 0.3V to 25V |

|----------------------------------------------------------------------------------|-------------|

| LX, PG, EN1, EN2 Voltage                                                         |             |

| BS-LX, FF, LDO Voltage                                                           |             |

| OUT Voltage                                                                      |             |

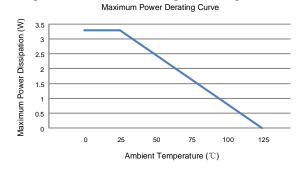

| Maximum Power Dissipation, $P_{D,MAX}$ , @ $T_A = 25 ^{\circ}\text{C}$ QFN3×3-20 | 3.3W        |

| Package Thermal Resistance (Note 2)                                              |             |

| $\theta$ Ja, QFN3×3-20                                                           | 30 ℃/W      |

| $\theta$ JC, QFN3 $\times$ 3-20                                                  | 4.5 ℃/W     |

| Junction Temperature Range                                                       |             |

| Lead Temperature (Soldering, 10 sec.)                                            | 260 ℃       |

| Storage Temperature Range                                                        |             |

| Dynamic LX Voltage in 10ns Duration                                              |             |

| <b>Recommended Operating Conditions</b> (Note 3)                                 |             |

| Supply Input Voltage                                                             | 4V to 23V   |

| Junction Temperature Range                                                       |             |

## **Electrical Characteristics**

$(V_{IN} = 12V, T_A = 25 \, \text{°C}, I_{OUT} = 1 \text{A unless otherwise specified})$

| $(V_{IN} = 12V, T_A = 25 \text{ C}, I_{OUT} = 12V, T_{A} = 25 \text{ C}, I_{OUT} = 12V, $ |                         |                                                                              | 3.6   | T     | M     | TT. 24            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------|-------|-------|-------|-------------------|

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Symbol                  | Test Conditions                                                              | Min   | Тур   | Max   | Unit              |

| Input Voltage Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>IN</sub>         |                                                                              | 4.0   |       | 23    | V                 |

| Input UVLO Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>UVLO</sub>       | V <sub>IN</sub> rising                                                       |       |       | 3.9   | V                 |

| Input UVLO Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $V_{HYS}$               |                                                                              |       | 0.3   |       | V                 |

| Quiescent Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $I_Q$                   | I <sub>OUT</sub> =0A, EN2=EN1=1,<br>V <sub>OUT</sub> =V <sub>SET</sub> ×105% |       | 80    | 100   | μA                |

| Shutdown Current 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I <sub>SHDN1</sub>      | EN1=0, EN2=1                                                                 |       |       | 65    | μA                |

| Shutdown Current 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I <sub>SHDN2</sub>      | EN1=0, EN2=0                                                                 |       | 6     | 10    | μA                |

| Output Voltage Set-point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $V_{SET}$               | CCM                                                                          | 3.305 | 3.338 | 3.371 | V                 |

| Top FET R <sub>DS(ON)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R <sub>DS(ON)1</sub>    |                                                                              |       | 85    |       | mΩ                |

| Bottom FET R <sub>DS(ON)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R <sub>DS(ON)2</sub>    |                                                                              |       | 35    |       | mΩ                |

| Output Discharge Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $I_{\mathrm{DIS}}$      | V <sub>OUT</sub> =3.338V                                                     |       | 50    |       | mA                |

| Top FET Current Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I <sub>LMT,TOP</sub>    |                                                                              | 8     |       |       | A                 |

| Bottom FET Current Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I <sub>LMT,BOT</sub>    |                                                                              | 6.5   |       |       | A                 |

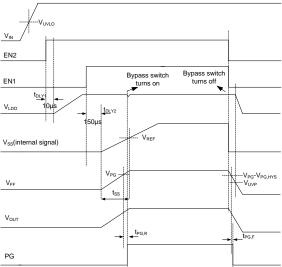

| Soft Start Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t <sub>SS</sub>         | V <sub>OUT</sub> from 0% to 100% V <sub>SET</sub>                            |       | 1.2   |       | ms                |

| EN2/EN1 Rising Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $V_{EN,R}$              | ~=-:                                                                         | 1.08  | 1.2   | 1.32  | V                 |

| EN2/EN1 Falling Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $V_{\rm EN.F}$          |                                                                              | 0.72  | 0.8   | 0.88  | V                 |

| Switching Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | f <sub>SW</sub>         | CCM                                                                          | 510   | 600   | 690   | kHz               |

| Min ON Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t <sub>ON,MIN</sub>     | V <sub>IN</sub> =V <sub>IN,MAX</sub>                                         | 010   | 50    | 0,0   | ns                |

| Min OFF Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t <sub>OFF,MIN</sub>    | V IIV V IIV,WAX                                                              |       | 150   |       | ns                |

| Output Over Voltage Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V <sub>OVP</sub>        | V <sub>FF</sub> rising                                                       | 115   | 120   | 125   | %V <sub>REF</sub> |

| Output Over Voltage Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V <sub>OVP,HYS</sub>    |                                                                              |       | 5     |       | %V <sub>REF</sub> |

| Output OVP Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t <sub>OVP,DLY</sub>    |                                                                              |       | 30    |       | μs                |

| Output Under Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |                                                                              |       |       |       | •                 |

| Protection Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $V_{UVP}$               |                                                                              | 55    | 60    | 65    | $%V_{REF}$        |

| Output UVP Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $t_{UVP,DLY}$           |                                                                              |       | 200   |       | μs                |

| Power Good Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $V_{PG}$                | V <sub>FF</sub> rising (Good)                                                | 88    | 90    | 94    | $%V_{REF}$        |

| Power Good Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $V_{PG,HYS}$            |                                                                              |       | 5     |       | $%V_{REF}$        |

| Power Good Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $t_{PG,R}$              | Low to high                                                                  |       | 200   |       | μs                |

| 1 owel Good Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $t_{PG,F}$              | High to low                                                                  |       | 10    |       | μs                |

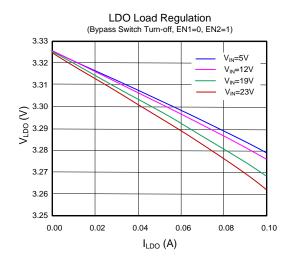

| LDO Output Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $V_{ m LDO}$            | $V_{IN}=12V, I_{LDO}=100mA$                                                  | 3.2   | 3.3   | 3.4   | V                 |

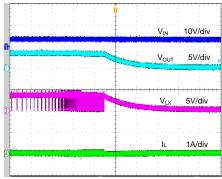

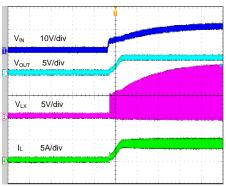

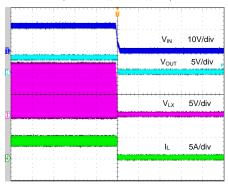

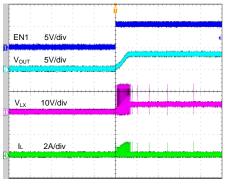

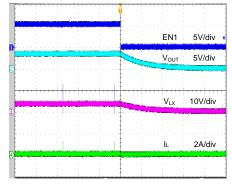

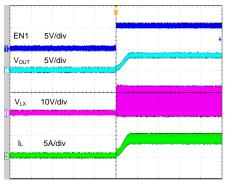

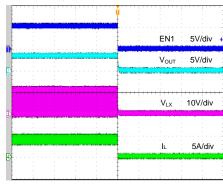

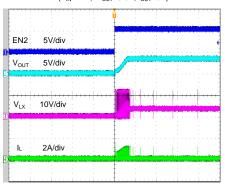

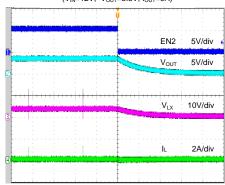

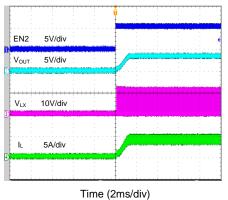

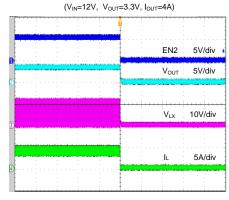

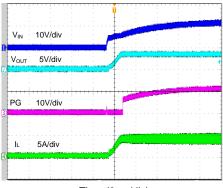

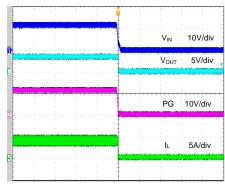

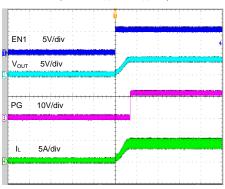

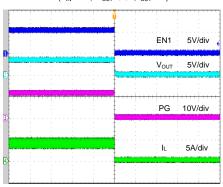

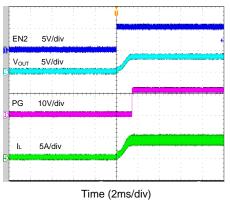

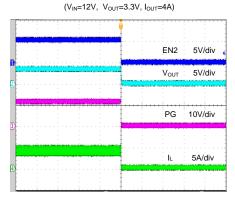

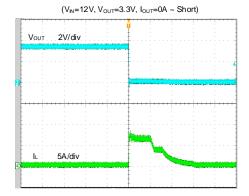

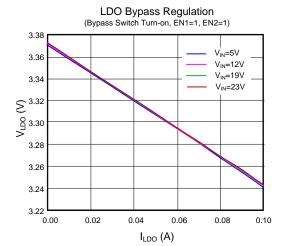

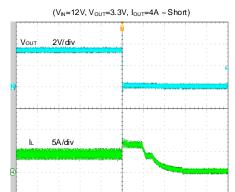

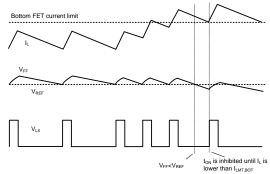

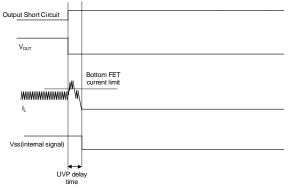

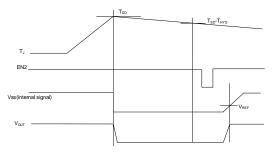

| LDO Dropout Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $V_{DROPOUT}$           | I <sub>LDO</sub> =100mA                                                      |       | 200   |       | mV                |