### High Efficiency Fast Response, 6A, 23V Input Synchronous Step Down Regulator

## **General Description**

The SY8286C develops a high efficiency synchronous step-down DC/DC regulator capable of delivering 6A current. The device integrates main switch and synchronous switch with very low  $R_{DS(ON)}$  to minimize the conduction loss.

The SY8286C has a fixed 5V DC/DC output and integrates a 5V 100mA LDO with bypass switch and individual enable control.

The SY8286C operates over a wide input voltage range from 5.5V to 23V. The DC/DC regulator adopts the instant PWM architecture to achieve fast transient responses for high step down applications and high efficiency at light loads. In addition, it operates at pseudo-constant frequency of 600kHz under heavy load conditions to minimize the size of inductor and capacitor.

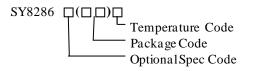

# **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY8286CRAC      | QFN3x3-20    |      |

### Features

- Low  $R_{DS(ON)}$  for Internal Switches (Top/Bottom): 38/19 m $\Omega$

- Wide Input Voltage Range: 5.5-23V

- 5V LDO with Individual Enable Control and Bypass Switch

- Integrated Bypass Switch: 1.5Ω

- Instant PWM Architecture to Achieve Fast Transient Responses

- Internal 1.2ms Soft-start Limits the Inrush Current

- Pseudo-constant Frequency: 600kHz.

- 6A Output Current Capability

- +/-1.5% Output Voltage Accuracy

- Power Good Indicator

- Output Discharge Function

- Output Current Limit Protection

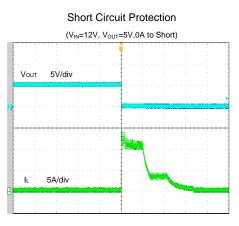

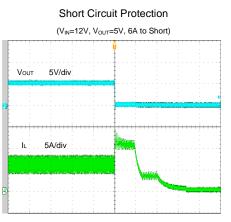

- Short Circuit Latch Off Protection

- Output Over Voltage Latch Off Protection

- Input UVLO

- Over Temperature Protection

- RoHS Compliant and Halogen Free

- Compact Package: QFN3x3-20

## Applications

- LCD-TV/Net-TV/3DTV

- Set Top Box

- Notebook

- High Power AP

100

(%)

Efficiency

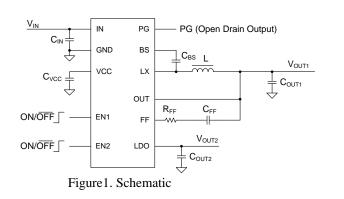

# **Typical Applications**

Silergy Corp. Confidential- Prepared for Customer Use Only 1 All Rights Reserved.

40

0.001

Load Current (A)

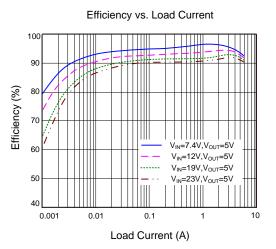

Figure2. Efficiency vs. Load Current

=7.4V.V

V<sub>IN</sub>=12V,V<sub>OUT</sub>=5V

V<sub>IN</sub>=19V,V<sub>OUT</sub>=5V

Efficiency vs. Load Current

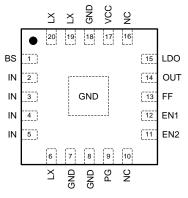

## Pinout (top view)

#### (QFN3x3-20)

Top Mark: AWW*xyz*, (Device code: AWW, *x=year code*, *y=week code*, *z= lot number code*)

| Pin Name | Pin Number | Pin Description                                                                     |  |  |

|----------|------------|-------------------------------------------------------------------------------------|--|--|

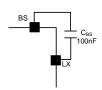

| BS       | 1          | Boot-strap pin. Supply high side gate driver. Decouple this pin to LX pin with a    |  |  |

|          |            | 0.1 µF ceramic capacitor.                                                           |  |  |

| IN       | 2,3,4,5    | Input pin. Decouple this pin to GND pin with at least a 10 µF ceramic cap.          |  |  |

| LX       | 6,19,20    | Inductor pin. Connect this pin to the switching node of inductor.                   |  |  |

| GND      | 7,8,18,EP  | Ground pin.                                                                         |  |  |

|          | 9          | PG is an open-drain output pin. This pin is externally pulled high when the output  |  |  |

| PG       |            | voltage is within 90% to 120% of regulation voltage range. Otherwise this pin is    |  |  |

|          |            | internally pull low.                                                                |  |  |

| NC       | 10,16      | Not connected.                                                                      |  |  |

| EN2      | 11         | Enable control of the IC and internal LDO. Pull this pin high to turn on the IC and |  |  |

| EINZ     |            | internal LDO. Do not leave this pin floating.                                       |  |  |

| EN1      | 12         | Enable control of the DC/DC regulator. Pull this pin high to turn on the regulator. |  |  |

| EINI     |            | Do not leave this pin floating.                                                     |  |  |

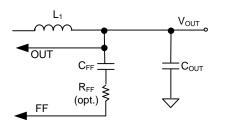

| FF       | 13         | Output feed forward pin. Connect RC network from the output to this pin.            |  |  |

| OUT      | 14         | Output pin. Connect to the output of DC/DC regulator. The pin also provides the     |  |  |

| OUT      |            | bypass input for internal LDO.                                                      |  |  |

| LDO      | 15         | 5V LDO output. Decouple this pin to ground with at least a 4.7 µF capacitor.        |  |  |

| VCC      | 17         | Internal 3.3V LDO output. Power supply for internal analog circuits and driving     |  |  |

| VCC      |            | circuit. Decouple this pin to GND with a 2.2 µF ceramic capacitor.                  |  |  |

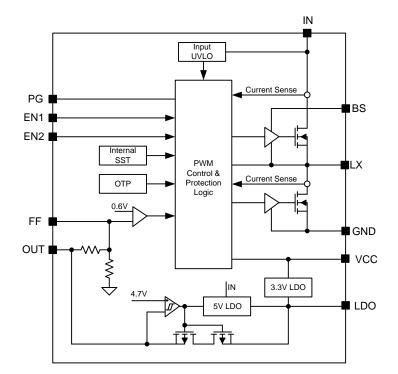

## **Block Diagram**

#### Figure3. Block Diagram

## Absolute Maximum Ratings (Note 1)

| IN, LX, PG                            | 25V      |

|---------------------------------------|----------|

| BS-LX                                 | 4V       |

| EN1, EN2                              | 25V      |

| VCC                                   | 4V       |

| LD0                                   | 6V       |

| OUT                                   | 6V       |

| FF                                    | 6V       |

| Power Dissipation,                    |          |

| $P_{D} @ T_{A} = 25 \ C \ QFN3x3-20$  | 3.3W     |

| Package Thermal Resistance (Note 2)   |          |

| θ ja, QFN3x3-20                       | 30 °C/W  |

| θ JC, QFN3x3-20                       | 4.5 °C/W |

| Junction Temperature Range            | 150 °C   |

| Lead Temperature (Soldering, 10 sec.) |          |

| Storage Temperature Range             |          |

| Dynamic LX Voltage in 10ns Duration   |          |

## Recommended Operating Conditions (Note 3)

| Supply Input Voltage       | 5.5V to 23V    |

|----------------------------|----------------|

|                            |                |

| Junction Temperature Range |                |

| Ambient Temperature Range  | 40 °C to 85 °C |

## **Electrical Characteristics**

$(V_{IN} = 12V, C_{OUT} = 100 \,\mu\text{F}, T_A = 25 \,\text{°C}, I_{OUT} = 1A$ , unless otherwise specified)

| Parameter Parameter                    | $I_A = 25 \text{ C}, I_{OU}$<br>Symbol | $_{\rm UT} = 1$ A, unless otherwise specif<br>Test Conditions | Min   | Тур | Max   | Unit               |

|----------------------------------------|----------------------------------------|---------------------------------------------------------------|-------|-----|-------|--------------------|

| Input Voltage Range                    | V <sub>IN</sub>                        |                                                               | 5.5   | Typ | 23    | V                  |

| Quiescent Current                      | IQ                                     | Iout=0, V <sub>OUT</sub> =V <sub>SET</sub> ×105%              | 5.5   | 108 | 145   | μA                 |

| Shutdown Current 1                     | I <sub>SHDN1</sub>                     | EN1=0, EN2=1                                                  |       | 59  | 70    | μΑ                 |

| Shutdown Current 2                     | I <sub>SHDN2</sub>                     | EN1=0, EN2=0                                                  |       | 6   | 10    | μΑ                 |

| Output Voltage Set-point               | V <sub>SET</sub>                       |                                                               | 5.023 | 5.1 | 5.177 | V                  |

| Top FET RON                            | R <sub>DS(ON)1</sub>                   |                                                               |       | 38  |       | mΩ                 |

| Bottom FET RON                         | R <sub>DS(ON)2</sub>                   |                                                               |       | 19  |       | mΩ                 |

| Output Discharge Current               | I <sub>DIS</sub>                       |                                                               |       | 70  |       | mA                 |

| HSFET FET Current Limit                | I <sub>LMT,HSFET</sub>                 |                                                               | 12    |     |       | А                  |

| Bottom FET Current Limit               | I <sub>LMT,LSFET</sub>                 |                                                               | 8     |     |       | А                  |

| Soft-start Time                        | tss                                    |                                                               |       | 1.2 |       | ms                 |

| EN Rising Threshold                    | V <sub>ENH</sub>                       |                                                               | 1     |     |       | V                  |

| EN Falling Threshold                   | V <sub>ENL</sub>                       |                                                               |       |     | 0.4   | V                  |

| Input UVLO Threshold                   | V <sub>UVLO</sub>                      |                                                               |       |     | 5     | V                  |

| UVLO hysteresis                        | V <sub>HYS</sub>                       |                                                               |       | 0.3 |       | V                  |

| Switching Frequency                    | Fosc                                   |                                                               | 510   | 600 | 690   | kHz                |

| Min ON Time                            | T <sub>ON,MIN</sub>                    | V <sub>IN</sub> =V <sub>INMAX</sub>                           |       | 50  |       | ns                 |

| Min OFF Time                           | T <sub>OFF,MIN</sub>                   |                                                               |       | 150 |       | ns                 |

| VCC Output                             | V <sub>CC</sub>                        | $V_{IN}=4V$                                                   | 3.2   | 3.3 | 3.4   | V                  |

| Output Over Voltage                    |                                        | V <sub>OUT</sub> rising                                       | 115   | 120 | 125   | $%V_{SET}$         |

| Threshold                              |                                        | VOUTISING                                                     | 115   | 120 | 125   | 70 V SET           |

| Output Over Voltage                    |                                        |                                                               |       | 2   |       | % V <sub>SET</sub> |

| Hysteresis                             |                                        |                                                               |       |     |       | 70 V 3E1           |

| Output OVP Delay                       |                                        |                                                               |       | 20  |       | μs                 |

| Output Under Voltage                   |                                        |                                                               | 45    | 50  | 55    | % V <sub>SET</sub> |

| Protection Threshold                   |                                        |                                                               |       | 200 | -     |                    |

| Output UVP Delay                       | <b>X</b> 7                             |                                                               |       | 200 | 0.0   | us                 |

| Power Good Threshold                   | V <sub>PG</sub>                        | V <sub>FB</sub> rising (good)                                 | 80    | 84  | 88    | % V <sub>REF</sub> |

| Power Good Hysteresis                  | V <sub>PG, HYS</sub>                   | Less to bish                                                  |       | 2   |       | % V <sub>REF</sub> |

| Power Good Delay                       | tpg, rising                            | Low to high                                                   |       | 200 |       | μs                 |

|                                        | tpg, falling                           | High to low                                                   | 4.95  | 10  | 5 15  | μs                 |

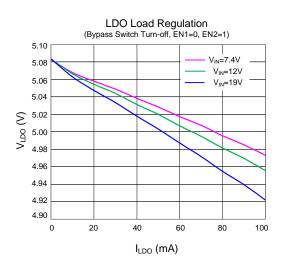

| LDO Output Voltage                     | V <sub>LDO</sub>                       | $V_{IN}=12V$ , no load                                        | 4.85  | 5   | 5.15  | V                  |

| LDO Dropout Voltage                    | VDROPOUT                               | I <sub>LDO</sub> =100mA                                       |       | 200 |       | mV                 |

| LDO Output Current<br>Limit            | I <sub>LMTLDO</sub>                    |                                                               | 150   |     | 300   | mA                 |

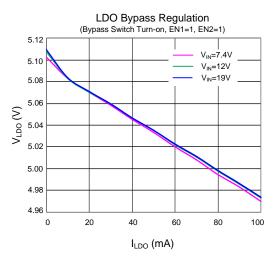

| Bypass Switch RON                      | R <sub>BYP</sub>                       |                                                               |       | 1.5 |       | Ω                  |

| Bypass Switch Turn-on                  | квур                                   |                                                               |       | 1.5 |       | 52                 |

| Voltage                                | V <sub>BYP</sub>                       |                                                               | 4.5   | 4.7 | 4.9   | V                  |

| Bypass Switch<br>Switchover Hysteresis |                                        |                                                               |       | 0.2 |       | V                  |

| Bypass Switch OVP                      |                                        |                                                               |       | 120 |       | %V <sub>LDO</sub>  |

| Thermal Shutdown                       | _                                      |                                                               |       |     |       |                    |

| Temperature                            | T <sub>SD</sub>                        |                                                               |       | 150 |       | C                  |

| Thermal Shutdown<br>Hysteresis         | Тнуѕ                                   |                                                               |       | 15  |       | C                  |

**Note 1**: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

Note 2:  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25 \ cmbox{C}$  on a four-layer Silergy Evaluation Board.

Note 3: The device is not guaranteed to function outside its operating conditions.

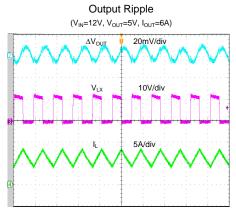

# **Typical Performance Characteristics**

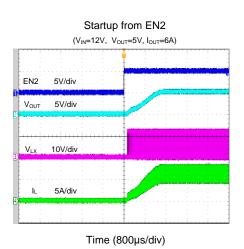

Load Transient (VIN=12V, VOUT=5V, IOUT=0.6-6A)

Time (200µs/div)

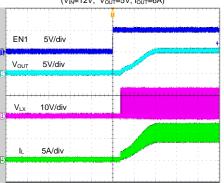

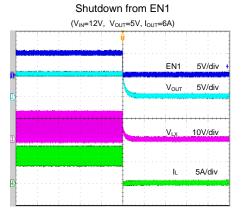

Startup from EN1 (V<sub>IN</sub>=12V, V<sub>OUT</sub>=5V, I<sub>OUT</sub>=6A)

Time (800µs/div)

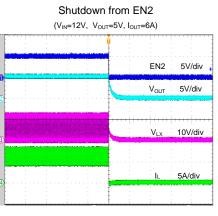

Time (400µs/div)

Time (400µs/div)

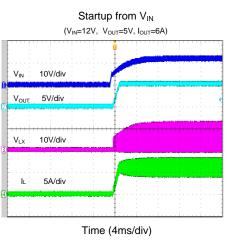

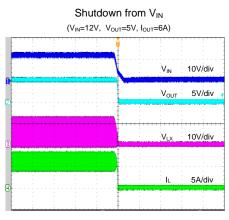

Time (4ms/div)

Time (100µs/div)

Time (2µs/div)

Time (100µs/div)

# Operation

The SY8286C develops a high efficiency synchronous step-down DC/DC regulator capable of delivering 6A current. The device integrates main switch and synchronous switch with very low  $R_{DS(ON)}$  to minimize the conduction loss.

The SY8286C has a fixed 5V DC/DC output and integrates a 5V 100mA LDO with bypass switch and individual enable control.

The SY8286C operates over a wide input voltage range from 5.5V to 23V. The DC/DC regulator adopts the instant PWM architecture to achieve fast transient responses for high step down applications and high efficiency at light loads. In addition, it operates at pseudo-constant frequency of 600kHz under heavy load conditions to minimize the size of inductor and capacitor.

# **Applications Information**

Because of the high integration in the SY8286C, the application circuit based on this regulator is rather simple. Only input capacitor  $C_{IN}$ , output capacitor  $C_{OUT}$  and output inductor L need to be selected for the targeted applications specifications.

#### Input Capacitor CIN:

The ripple current through input capacitor is calculated as:

$I_{_{\rm CIN\_RMS}} = I_{_{\rm OUT}} \cdot \sqrt{D(1-D)} \cdot$

To minimize the potential noise problem, place a typical X5R or better grade ceramic capacitor really close to the IN and GND pins. Care should be taken to minimize the loop area formed by  $C_{IN}$ , and IN/GND pins. In this case, a 10uF low ESR ceramic capacitor is recommended.

#### **Output Capacitor Cour:**

The output capacitor is selected to handle the output ripple noise requirements. Both steady state ripple and transient requirements must be taken into consideration when selecting this capacitor. For most applications, an X5R or better grade ceramic capacitor greater than  $66\,\mu\text{F}$  capacitance can work well. The capacitance derating with DC voltage must be considered.

#### **Output Inductor L:**

There are several considerations in choosing this inductor.

1) Choose the inductance to provide the desired ripple current. It is suggested to choose the ripple current to be about 40% of the maximum output current. The inductance is calculated as:

$$L = \frac{V_{\text{OUT}}(1 - V_{\text{OUT}}/V_{\text{IN,MAX}})}{F_{\text{SW}} \times I_{\text{OUT,MAX}} \times 40\%}$$

Where  $F_{\text{SW}}$  is the switching frequency and  $I_{\text{OUT,MAX}}$  is the maximum load current.

The SY8286C regulator IC is quite tolerant of different ripple current amplitude. Consequently, the final choice of inductance can be slightly off the calculation value without significantly impacting the performance.

2) The saturation current rating of the inductor must be selected to be greater than the peak inductor current under full load conditions.

$$I_{SAT, MIN} > I_{OUT, MAX} + \frac{V_{OUT}(1-V_{OUT}/V_{IN, MAX})}{2 \cdot F_{SW} \cdot L}$$

3) The DCR of the inductor and the core loss at the switching frequency must be low enough to achieve the desired efficiency requirement. It is desirable to choose an inductor with DCR<10m $\Omega$  to achieve a good overall efficiency.

#### Soft-start

The SY8286C has a built-in soft-start to control the rise rate of the output voltage and limit the input current surge during IC start-up. The typical soft-start time is 1.2ms.

#### **Enable Operation**

The device contains two enable pins to control the LDO and buck regulator. Driving EN2 pin high (>1V) enables the IC and the LDO. To enable the buck regulator, both EN1 and EN2 should be driven high. When EN1 and EN2 are driven below 0.4V, the device will be shut down, reducing input current <10uA. For automatic start-up, connect enable pins to VIN directly or through a 100k resistor.

#### External Bootstrap Cap

This capacitor provides the gate driver voltage for internal high side MOSEFET. A 100nF low ESR ceramic capacitor connected between BS pin and LX pin is recommended.

# AN\_SY8286C

#### VCC LDO

The 3.3V VCC LDO provides the power supply for internal control circuit. Bypass this pin to ground with a  $2.2 \,\mu$ f ceramic capacitor.

#### <u>LDO</u>

Internal 5V LDO output. Power supply for internal analog circuit and driving circuit. This pin should be bypassed to ground with a 4.7uf ceramic capacitor. This pin is also capable sourcing 100mA current for external load.

#### **Power Good Indication**

PG is an open-drain output pin. This pin will pull to ground if output voltage is lower than 90% of regulation voltage. Otherwise this pin will go to a high impedance state.

#### Load Transient Considerations:

The SY8286C regulator IC adopts the instant PWM architecture to achieve good stability and fast transient responses. In applications with high step load current, adding an RC network  $R_{FF}$  and  $C_{FF}$  between OUT and FF pin may further speed up the load transient responses.

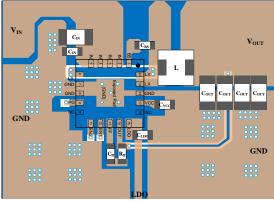

#### Layout Design:

The layout design of SY8286C regulator is relatively simple. For the best efficiency and to minimize noise problem, we should place the following components close to the IC:  $C_{IN}$ ,  $C_{LDO}$ ,  $C_{VCC}$ , L.

- 1) It is desirable to maximize the PCB copper area connecting to GND pin to achieve the best thermal and noise performance. If the board space allowed, a ground plane is highly desirable.

- 2) C<sub>IN</sub> must be close to Pins IN and GND. The loop area formed by C<sub>IN</sub> and GND must be minimized.

- The PCB copper area associated with LX pin must be minimized to avoid the potential noise problem.

- 4) If the system chip interfacing with the enable pin has a high impedance state at shutdown mode and the IN pin is connected directly to a power source such as a Li-Ion battery, A 1Mohm pull down resistor should be placed between the enable pin and GND pins to prevent the noise from falsely turning on the regulator at shutdown mode.

# AN\_SY8286C

Figure4. PCB Layout Suggestion

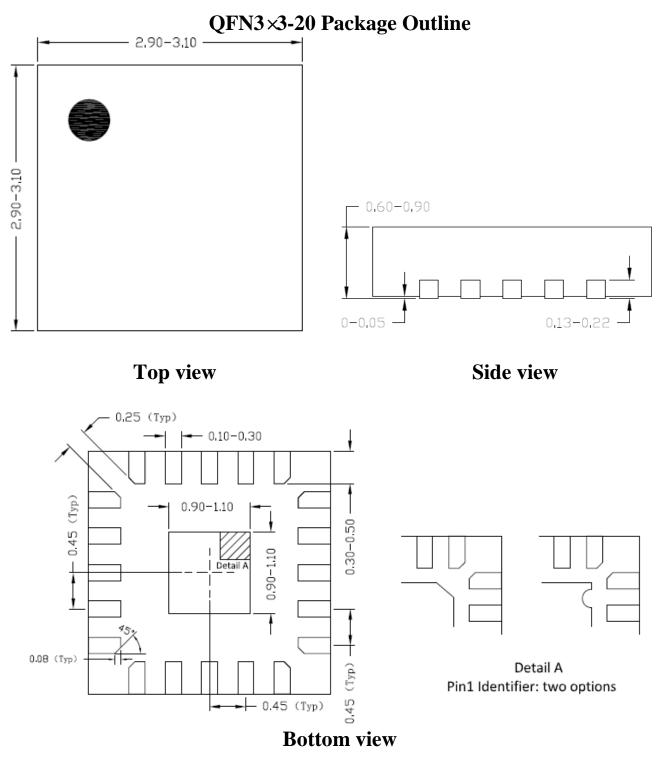

Notes: All dimension in millimeter and exclude mold flash & metal burr.

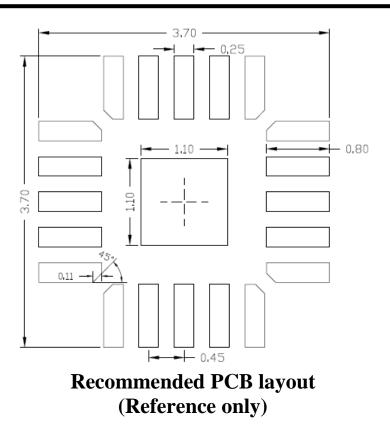

# **Taping & Reel Specification**

## 1. QFN3×3-20 taping orientation

## 2. Carrier Tape & Reel specification for packages

|    | ackage | Tape width | Pocket    | Reel size | Trailer    | Leader length | Qty per |

|----|--------|------------|-----------|-----------|------------|---------------|---------|

|    | types  | (mm)       | pitch(mm) | (Inch)    | length(mm) | (mm)          | reel    |

| QI | FN3×3  | 12         | 8         | 13"       | 400        | 400           | 5000    |

## 3. Others: NA

# **Revision History**

The revision history provided is for informational purpose only and is believed to be accurate, however, not warranted. Please make sure that you have the latest revision.

| Date           | Revision      | Change                                                                                                                                                                                      |

|----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nov 21, 2019   | Revision 0.9I | Update "Power Good Threshold" in EC table                                                                                                                                                   |

| Jan 17, 2018   | Revision 0.9H | Add "Revision History" in page 13, Important Notice in page 14.                                                                                                                             |

| July 18, 2017  | Revision 0.9G | Update "Power good indicator" in page 10.                                                                                                                                                   |

| May 30, 2016   | Revision 0.9F | Update package outline (Recommended PCB layout)                                                                                                                                             |

| May 5, 2016    | Revision 0.9E | Update package outline (side view)                                                                                                                                                          |

| April 13, 2016 | Revision 0.9D | Update the data in EC table (I_Q, I_{SHDN}, I_{Discharge,} V_{ENH}, V_{HYS}, V_{PG} threshold/ HYS, $V_{LDO}$                                                                               |

| Dec 31, 2015   | Revision 0.9C | Update general description.                                                                                                                                                                 |

| Nov 26, 2015   | Revision 0.9B | <ol> <li>Features: Change "+/-1% Internal Vref" to "+/-1.5% output<br/>voltage accuracy"</li> <li>PG pin description</li> <li>Enable Operation in Application Information(Page9)</li> </ol> |

| July 15, 2015  | Revision 0.9A | Add " dynamic LX voltage" in Abs (Page3)                                                                                                                                                    |

| July 12, 2015  | Revision 0.9  | Initial Release                                                                                                                                                                             |

#### **IMPORTANT NOTICE**

1. **Right to make changes.** Silergy and its subsidiaries (hereafter Silergy) reserve the right to change any information published in this document, including but not limited to circuitry, specification and/or product design, manufacturing or descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to Silergy's standard terms and conditions of sale.

2. Applications. Application examples that are described herein for any of these products are for illustrative purposes only. Silergy makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Buyers are responsible for the design and operation of their applications and products using Silergy products. Silergy or its subsidiaries assume no liability for any application assistance or designs of customer products. It is customer's sole responsibility to determine whether the Silergy product is suitable and fit for the customer's applications and products planned. To minimize the risks associated with customer's products and applications, customer should provide adequate design and operating safeguards. Customer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Silergy assumes no liability related to any default, damage, costs or problem in the customer's applications or products, or the application or use by customer's third-party buyers. Customer will fully indemnify Silergy, its subsidiaries, and their representatives against any damages arising out of the use of any Silergy components in safety-critical applications. It is also buyers' sole responsibility to warrant and guarantee that any intellectual property rights of a third party are not infringed upon when integrating Silergy products into any application. Silergy assumes no responsibility for any said applications or for any use of any circuitry other than circuitry entirely embodied in a Silergy product.

3. Limited warranty and liability. Information furnished by Silergy in this document is believed to be accurate and reliable. However, Silergy makes no representation or warranty, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. In no event shall Silergy be liable for any indirect, incidental, punitive, special or consequential damages, including but not limited to lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges, whether or not such damages are based on tort or negligence, warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, Silergy' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Standard Terms and Conditions of Sale of Silergy.

4. **Suitability for use.** Customer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of Silergy components in its applications, notwithstanding any applications-related information or support that may be provided by Silergy. Silergy products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Silergy product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Silergy assumes no liability for inclusion and/or use of Silergy products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

5. **Terms and conditions of commercial sale**. Silergy products are sold subject to the standard terms and conditions of commercial sale, as published at http://www.silergy.com/stdterms, unless otherwise agreed in a valid written individual agreement specifically agreed to in writing by an authorized officer of Silergy. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Silergy hereby expressly objects to and denies the application of any customer's general terms and conditions with regard to the purchase of Silergy products by the customer.

6. No offer to sell or license. Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights. Silergy makes no representation or warranty that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right. Information published by Silergy regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from Silergy under the patents or other intellectual property of Silergy.

For more information, please visit: www.silergy.com

#### © 2019 Silergy Corp.

All Rights Reserved.