### SY2A58152 Twelve Half -bridge Driver with SPI Control

### **General Description**

The SY2A58152 is a twelve half-bridge motor driver solution for automotive, industrial and other mechatronic applications. The half-bridges are fully controllable to achieve a forward, reverse, coasting and braking operation of motor. All the functions can be programmed through serial peripheral interface (SPI).

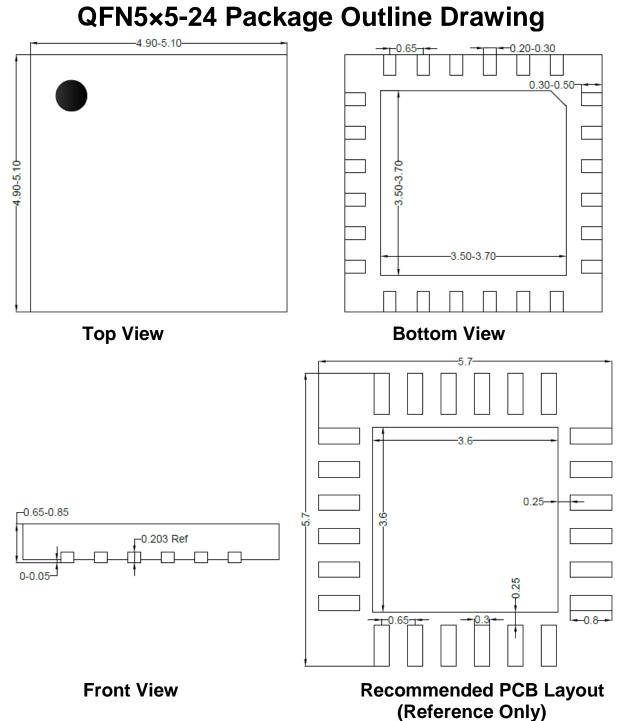

The SY2A58152 provides internal shutdown functions with an nFAULT output pin to alert the system when a fault occurs. Such as over current protection, open load detection, under voltage lockout, over voltage lockout and thermal shutdown. The device is packaged in QFN5x5-24 with exposed pad.

### **Ordering Information**

SY2A58152 中(ロロロ)

Package Code

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY2A58152VAQ    | QFN5×5-24    |      |

### Features

- 12 Half-bridge Outputs

- 4.5V to 32V Operating Voltage

- Up to 1A RMS Output Current for Each Output

- Low-power Sleep Mode

- Compatible with 5V/3.3V System

- Serial Peripheral Interface, up to 5MHz;

- Daisy Chain Functionality

- PWM Capable Output for Frequency 80Hz, 100Hz, 200Hz and 2kHz with 8-Bit Duty Cycle Resolution

- Integrated Protection: Overcurrent Protection (OCP), Short Circuit Protection (SCP), Open Load Detection (OLD), Under Voltage Lockout (UVLO), Over Voltage Protection (OVP) and Thermal Shutdown (TSD)

- nFAULT Pin Output

- AEC-Q100 Qualified

## Applications

- Automotive

- HVAC

- DC brushed motors

- LED

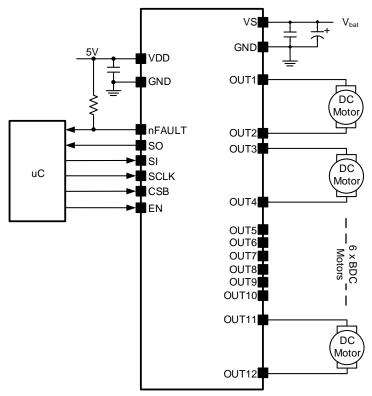

# **Typical Application**

Figure 1. Typical Application Circuit

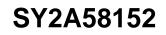

(QFN5×5-24)

#### Top Mark: FWWxyz (device code: FWW, x=year code, y=week code, z= lot number code)

| Pin Name | Pin No. | Pin Description                                                                                                          |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------|

| OUT12    | 1       | Half-bridge Output 12.                                                                                                   |

| OUT3     | 2       | Half-bridge Output 3.                                                                                                    |

| VS       | 3,4     | Power supply for internal high side output drivers.                                                                      |

| OUT2     | 5       | Half-bridge Output 2.                                                                                                    |

| OUT11    | 6       | Half-bridge Output 11.                                                                                                   |

| OUT1     | 8       | Half-bridge Output 1.                                                                                                    |

| OUT7     | 9       | Half-bridge Output 7.                                                                                                    |

| OUT9     | 10      | Half-bridge Output 9.                                                                                                    |

| OUT5     | 11      | Half-bridge Output 5.                                                                                                    |

| EN       | 12      | Enable. Logic high enables the IC. Internal pull down.                                                                   |

| SO       | 13      | Serial data output. 16-bit serial communications output.                                                                 |

| VDD      | 14      | Power supply for internal logic.                                                                                         |

| GND      | 7,15,24 | Ground. Internal connection to lead frame.                                                                               |

| CSB      | 17      | Chip select Bar. Active low serial port operation.                                                                       |

| SCLK     | 18      | Serial Clock. Clock input for use with SPI communication.                                                                |

| SI       | 19      | Serial input. 16-bit serial communications input.                                                                        |

| OUT6     | 20      | Half-bridge Output 6.                                                                                                    |

| OUT10    | 21      | Half-bridge Output 10.                                                                                                   |

| OUT8     | 22      | Half-bridge Output 8.                                                                                                    |

| OUT4     | 23      | Half-bridge Output 4.                                                                                                    |

| nFAULT   | 16      | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pull-up resistor. |

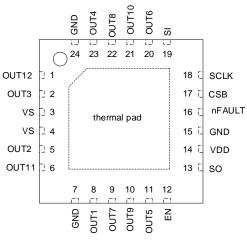

## **Function Block**

## Absolute Maximum Ratings (Note 1)

| VS (DC)                                       | 0.3V to 40V    |

|-----------------------------------------------|----------------|

| OUTx (DC)                                     |                |

| Digital pin (SI, SCLK, CS, SO, EN, nFAULT)    |                |

| VDD                                           | 0.3V to 5.75 V |

| Continuous supply current (VS pins) (Note 2)  | 0A to 6A       |

| Continuous sink current (GND pins) (Note 2)   | 0A to 6A       |

| Junction Temperature (T <sub>J</sub> )        |                |

| Storage Temperature                           | 65°C to 150°C  |

| QFN5x5-24 Package Thermal Resistance (Note 3) |                |

| $\theta$ <sub>JA</sub>                        | 22°C/W         |

| $\theta_{\text{ JC TOP}}$                     | 12°C/W         |

## **Recommended Operating Conditions**

| VS                                      | 4.5V to 32V   |

|-----------------------------------------|---------------|

| VDD                                     | 3.15V to 5.5V |

| Digital pin                             | 0V to 5.5V    |

| nFAULT pullup voltage                   |               |

| nFAULT output current                   | 0V to 5mA     |

| Operating Temperature (T <sub>A</sub> ) |               |

| Junction Temperature (TJ)               |               |

|                                         |               |

## **Electrical Characteristics**

(-40°C <T<sub>A</sub> < 125°C, 4.5V< VS <32V, 3.15V<VDD<5.5V, EN=VDD, unless otherwise specified)

| Parameter                          | Symbol                                          | Test Conditions                                 | Min      | Тур  | Max        | Uni     |

|------------------------------------|-------------------------------------------------|-------------------------------------------------|----------|------|------------|---------|

| Power Supplies                     |                                                 |                                                 |          |      | -          |         |

| VS Sleep Mode Current              | IVS_sleep                                       | VS =13.5V, EN=L, T <sub>A</sub> =25°C           |          | 0.35 | 1          | μA      |

|                                    | 100_3666                                        | VS =13.5V, EN=L, T <sub>A</sub> =125°C          |          |      | 4.5        | μA      |

| VS Standby Mode Current            | he i i                                          | VS=13.5V, EN=H, Driver=OFF, TA=25°C             |          | 0.5  | 0.7        | mA      |

|                                    | VS_standby                                      | VS=13.5V, EN=H, Driver=OFF, TA=125°C            |          |      | 0.7        | mA      |

|                                    |                                                 | VS=13.5V, EN=H, All High-Side                   |          | 2.6  | 4          | mA      |

| VS Operating Mode Current          | lvs                                             | FETs=ON, T <sub>A</sub> =25°C                   |          | 2.0  | •          |         |

|                                    |                                                 | VS=13.5V, EN=H, All High-Side                   |          |      | 4          | mA      |

|                                    | N                                               | FETs=ON, TA=125°C                               | 2.0      |      | 4.0        | V       |

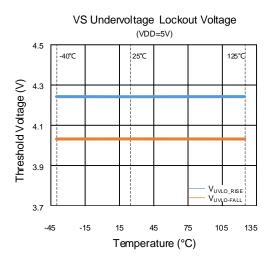

| VS Undervoltage Lockout Voltage    | VUVLO_FALL                                      | VS falling<br>VS rising                         | 3.8<br>4 |      | 4.3<br>4.5 | V       |

| vs ondervollage Lockoul vollage    | V <sub>UVLO_RISE</sub><br>V <sub>UVLO_HYS</sub> | vonsing                                         | 4        | 200  | 4.0        | v<br>m∖ |

| VS Undervoltage Lockout Deglitch   | VUVLO_HYS                                       |                                                 |          |      |            |         |

| Time                               | <b>t</b> uvlo                                   |                                                 |          | 10   |            | μs      |

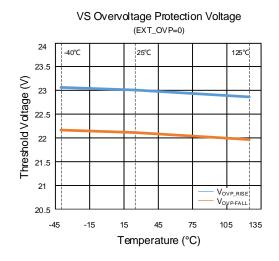

|                                    |                                                 | VS rising, EXT_OVP=0b                           | 21       |      | 25         | V       |

|                                    | .,                                              | VS falling, EXT_OVP=0b                          | 20       |      | 24         | V       |

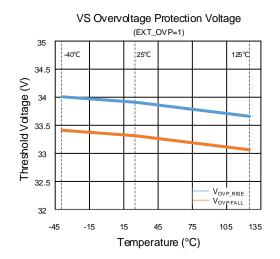

|                                    | Vovp                                            | VS rising, EXT_OVP=1b                           | 32.6     |      | 35.1       | V       |

| VS Overvoltage Protection          |                                                 | VS falling, EXT_OVP=1b                          | 32       |      | 34.5       | V       |

|                                    |                                                 | Rising to falling threshold, EXT_OVP=0b         |          | 1    |            | V       |

|                                    | Vovp_hys                                        | Rising to falling threshold, EXT_OVP=1b         |          | 0.7  |            | V       |

| VS Overvoltage Protection Deglitch | tour                                            |                                                 |          |      |            |         |

| Time                               | tovp                                            |                                                 |          | 10   |            | μs      |

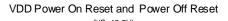

| VDD Power On Reset Threshold       | VPOR_ON                                         | Supply rising                                   | 2.75     |      | 3.05       | V       |

| VDD Power Off Reset Threshold      | VPOR_OFF                                        | Supply falling                                  | 2.6      |      | 2.9        | V       |

| POR Undervoltage Hysteresis        | VPOR_HYS                                        | Rising to falling threshold                     |          | 150  |            | m١      |

|                                    |                                                 | VS=13.5V, VDD=3.3V, EN=H,                       |          | 3.5  | 5          | m/      |

|                                    |                                                 | all low-side FETs=ON, SPI=ON, TA=25°C           |          | 5.5  | 5          | 111/    |

| VDD Operating Supply Current       | I <sub>VDD</sub>                                | VS =13.5V, VDD=3.3V, EN=H,                      |          |      |            |         |

|                                    |                                                 | all low-side FETs=ON, SPI=ON,                   |          |      | 5          | m/      |

|                                    |                                                 | T <sub>A</sub> =125°C                           |          |      |            |         |

|                                    |                                                 | VS=13.5V, VDD=3.3V, EN=H,SPI=OFF,               |          | 2    | 3          | m/      |

| VDD Standby Mode Current           | VDD_standby                                     |                                                 |          |      |            |         |

| 5                                  |                                                 | VS=13.5V, VDD=3.3V, EN=H,SPI=OFF,               |          |      | 3          | m/      |

|                                    |                                                 | T <sub>A</sub> =125°C                           |          | 1 1  | 2          |         |

| VDD Sleep Mode Current             | IVDD_sleep                                      | VS=13.5V, VDD=3.3V, EN=L, T <sub>A</sub> =25°C  |          | 1.1  | 2          | μΑ      |

| Logic Level Input (EN, SI, SCLK, C |                                                 | VS=13.5V, VDD=3.3V, EN=L, T <sub>A</sub> =125°C |          |      | 2          | μA      |

| nput Low Voltage                   | VIL                                             |                                                 | 0        |      | 0.6        |         |

| nput High Voltage                  | VIL                                             |                                                 | 2        |      | 0.0        | V       |

| nput Logic Hysteresis              | VIN                                             |                                                 | 200      |      |            | m١      |

| nput Low Current                   |                                                 | VIN=0V                                          | -1       |      | 1          | μA      |

| nput High Current                  | Ін                                              | VIN=VDD                                         |          | 60   | 100        | μA      |

| nput Capacitance                   | CCAPINX                                         | (Note 4)                                        |          | -    | 15         | pF      |

| Open-Drain Output(nFAULT)          | COALINA                                         |                                                 |          |      |            | - P·    |

| Output Low Voltage                 | Vol                                             | I <sub>sink</sub> =5mA                          | 0        |      | 0.4        | V       |

| Output High Current                | Іон                                             | Vod=5V                                          | -1       |      | 1          | μA      |

| Output Capacitance                 | COD                                             | (Note 4)                                        | -        | -    | 15         | pF      |

| Push-pull Output (SO) (Note 4)     |                                                 |                                                 |          |      |            |         |

| Output Low Voltage                 | Vol                                             | I <sub>out</sub> = -5mA (Note 4)                | 0        |      | 0.4        | V       |

| Output High Voltage                |                                                 |                                                 | VDD-     |      | VDD        | V       |

|                                    | Vон                                             | I <sub>out</sub> = 5mA (Note 4)                 | 0.6      |      | 000        | V       |

| Output Capacitance                 | COD                                             | (Note 4)                                        |          |      | 30         | pF      |

| Dutput Low Current                 | lol                                             | V <sub>SO</sub> =0V                             | -1       |      | 1          | μA      |

| Output High Current                | I <sub>OH</sub>                                 | V <sub>SO</sub> =VDD                            | -1       |      | 1          | μA      |

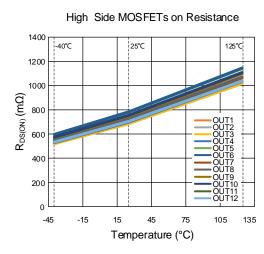

| Power MOSFETs                      | 1                                               |                                                 | I.       | 1    | r          |         |

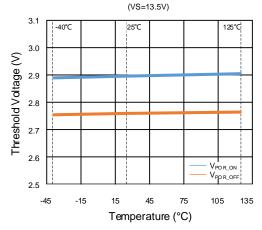

| High Side FETs on Resistance       | RDSON                                           | I <sub>out</sub> =500mA VS=13.5V                |          | 0.75 | 1.6        | Ω       |

| Low Side FETs on Resistance        | I VDSON                                         | I <sub>out</sub> =500mA VS=13.5V                | 1        | 0.75 | 1.6        | 32      |

# SY2A58152

| Output Rise and Fall Time                              |                    | VS=13.5V,10-90% R <sub>LOAD</sub> =27Ω,<br>HBx_SR=0b                                                     |             | 1          |            | V/µs     |

|--------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------|-------------|------------|------------|----------|

| (HS&LS)                                                | SLrise and fall    | VS=13.5V,10-90% R <sub>LOAD</sub> =27Ω,<br>HBx_SR=1b                                                     |             | 3.7        |            | V/µs     |

| Output Dead Time (High to Low /                        |                    | VS =13.5V, SR=0, HS/LS driver OFF to LS/HS driver ON                                                     | 6           | 15         | 25         | μs       |

| Low to High)                                           | <b>t</b> DEAD      | VS =13.5V, SR=1, HS/LS driver OFF to LS/HS driver ON                                                     | 2           | 5          | 15         | μs       |

| Propagation Delay (Hide-side and                       | <b>t</b>           | High-side ON or low-side ON command<br>(SPI last transition) to OUTx transition<br>from Hi-Z state, SR=0 | 3           | 6          | 15         | μs       |

| Low-side ON/OFF)                                       | t <sub>PD</sub>    | High-side ON or low-side ON command<br>(SPI last transition) to OUTx transition<br>from Hi-Z state, SR=1 | 1           | 3          | 8          | μs       |

| Source Leakage Current                                 | Isource LC         | OUTx=0V, EN=1                                                                                            |             | 6          | 10         | μA       |

| Course Loanage Current                                 | 1300100_20         | OUTx=0V, EN=0                                                                                            |             |            | 2          | μA       |

|                                                        |                    | OUTx=13.5V, EN=1, SR=0b                                                                                  |             | 13.5       | 20         | μA       |

| Sink Leakage Current                                   | sink_LC            | OUTx=13.5V, EN=1, SR=1b                                                                                  |             | 13.5       | 20         | μA       |

|                                                        |                    | OUTx=13.5V, EN=0, SR=0b                                                                                  |             |            | 2          | μA       |

| PWM Mode                                               |                    |                                                                                                          | 50          | 00         | 101        |          |

|                                                        | fрwм               | PWM_CHx_FREQ=00b                                                                                         | 56          | 80         | 104        | Hz       |

| PWM Switching Frequency                                |                    | PWM_CHx_FREQ=01b<br>PWM_CHx_FREQ=10b                                                                     | 70          | 100<br>200 | 130<br>260 | Hz<br>Hz |

|                                                        |                    | PWM_CHx_FREQ=100<br>PWM_CHx_FREQ=11b                                                                     | 140<br>1400 | 200        | 260        | HZ       |

| Protections                                            |                    |                                                                                                          | 1400        | 2000       | 2000       | 112      |

| Thermal Warning Temperature                            | Twarn              | (Note 4)                                                                                                 | 120         | 140        | 170        | °C       |

| Thermal Warning Hysteresis                             | TWARN<br>TWARN_HYS | (Note 4)                                                                                                 | 120         | 20         | 170        | 0°       |

| Thermal Shutdown Temperature                           | Twarn_HYS          | (Note 4)                                                                                                 | 150         | 165        | 185        | °C       |

| Thermal Shutdown Hysteresis                            | THYS               | (Note 4)                                                                                                 | 150         | 20         | 105        | °C       |

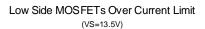

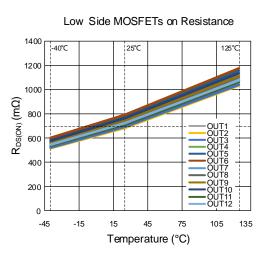

| Over Current Shutdown Threshold                        | THYS               |                                                                                                          |             | 20         |            | U U      |

| (Source)                                               | locso              | VDD=5V, VS=13.5V                                                                                         | -2.3        | -1.8       | -1.3       | A        |

| Over Current Shutdown Threshold (Sink)                 | locsi              | VDD=5V, VS=13.5V                                                                                         | 1.3         | 1.8        | 2.3        | А        |

|                                                        |                    | OCP_DEG=000b                                                                                             | 6           | 10         | 14.5       | μs       |

|                                                        |                    | OCP_DEG=001b(Note 4)                                                                                     | 2.6         | 5          | 7.9        | μs       |

|                                                        |                    | OCP_DEG=010b(Note 4)                                                                                     | 0.4         | 2.5        | 5.9        | μs       |

| Over Current Shutdown Delay                            |                    | OCP_DEG=011b                                                                                             | 0.1         | 1          | 3.4        | μs       |

| Time                                                   | t <sub>oc</sub>    | OCP_DEG=100b                                                                                             | 38.2        | 60         | 80         | μs       |

|                                                        |                    | OCP_DEG=101b(Note 4)                                                                                     | 23.1        | 40         | 51.9       | μs       |

|                                                        |                    | OCP_DEG=110b(Note 4)                                                                                     | 18.5        | 30         | 41.5       | μs       |

|                                                        |                    | OCP_DEG=111b(Note 4)                                                                                     | 8.4         | 20         | 31.6       | μs       |

| Open Load Detection Current                            | Iold               | High-side or Low side                                                                                    | 2           | 9          | 18         | mA       |

| Open Load Detection Current in<br>Low Current OLD Mode | Iold_low           | Low side                                                                                                 | 0.2         | 0.8        | 2          | mA       |

| Open Load Detection Delay Time                         | told               | Continuous Mode                                                                                          | 2.2         | 3          | 3.8        | ms       |

| Open Load Delection Delay Time                         | IULD               | PWM Mode                                                                                                 | 150         | 200        | 300        | μs       |

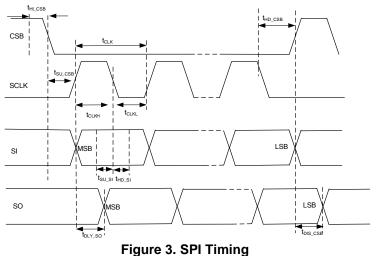

# **Serial Peripheral Interface**

(-40°C <T<sub>A</sub> < 125°C, 4.5V< VS <32V, 3.15V<VDD<5.5V, EN=VDD, unless otherwise specified)

| Parameter                                  | Symbol                | Test Conditions                                              | Min | Тур | Max | Unit |

|--------------------------------------------|-----------------------|--------------------------------------------------------------|-----|-----|-----|------|

| SCLK Frequency                             | f <sub>CLK</sub>      | (Note 4)                                                     |     |     | 5   | MHz  |

| SCLK High Time                             | <b>t</b> CLKH         | (Note 4)                                                     | 100 |     |     | ns   |

| SCLK Low Time                              | <b>t</b> CLKL         | (Note 4)                                                     | 100 |     |     | ns   |

| SI Setup Time                              | tsu_si                | (Note 4)                                                     | 40  |     |     | ns   |

| SI Hold Time                               | t <sub>HD_SI</sub>    | (Note 4)                                                     | 60  |     |     | ns   |

| SO Output Data Delay Time                  | tDLY_SO               | SCLK high to SO valid(Note 4)                                |     |     | 60  | ns   |

| CSB Setup Time                             | tsu_csв               | (Note 4)                                                     | 100 |     |     | ns   |

| CSB Hold Time                              | <b>t</b> нD_CSB       | (Note 4)                                                     | 100 |     |     | ns   |

| CSB Disable Delay Time                     | t <sub>DIS_CSB</sub>  | CSB high to SO High-Z (Note 4)                               |     | 30  |     | ns   |

| CSB Minimum High Time<br>before Active Low | tнı_csв               | (Note 4)                                                     | 600 |     |     | ns   |

| EN Low Valid Time                          | t <sub>ENL</sub>      | VDD=5V, EN going low 50% to<br>OUTx turning off 50% (Note 4) | 10  |     |     | μs   |

| EN High to SPI Valid                       | t <sub>ENH_SPIV</sub> | (Note 4)                                                     |     |     | 100 | μs   |

**Note 1**: Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied.

Note 2: Power dissipation and thermal limits must be observed.

**Note 3:**  $\theta_{JA}$  are measured under the natural convention at  $T_A = 25^{\circ}C$  on a highly effective four layer thermal conductivity test board with thermal via.

Note 4: Guaranteed by design.

### **Typical Performance Characteristics**

High Side MOSFETs Over Current Limit (VS=13.5V)

# SY2A58152

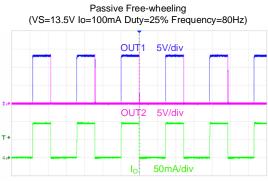

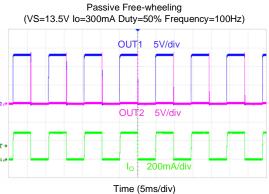

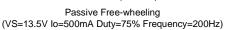

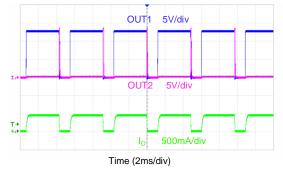

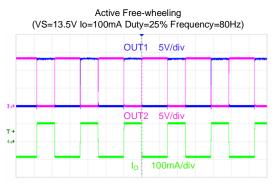

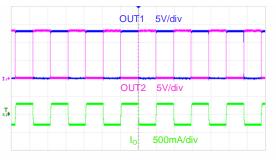

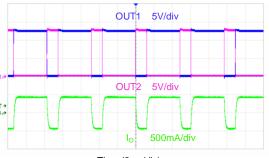

### **Operation Waveform**

Time (5ms/div)

Time (5ms/div)

Active Free-wheeling (VS=13.5V lo=300mA Duty=50% Frequency=100Hz)

Time (5ms/div) Active Free-wheeling (VS=13.5V Io=500mA Duty=75% Frequency=200Hz)

Time (2ms/div)

## **Function Description**

The SY2A58152 is a twelve half-bridge motor driver solution for automotive, industrial and other mechatronic applications. It can be configured as 6 independent H-bridges. The half-bridges are designed to support 1-A per half-bridge.

The device supports a standard 16-bit, 5-MHz serial peripheral interface (SPI). The device is also equipped with a daisychain functionality which allows connecting multiple devices using a single CSB line and saving on multiple resources.

#### **Power Supply**

VS powers the MOSFETs, and VDD powers the logic circuits. After the VS power up, the drivers are allowed to turn on. All the drivers are initialized in the off condition, and remain off regardless of VDD status. VDD power up resets all the internal logic. All the internal registers are cleared on VDD POR.

#### **Driving Control**

The device can be configured as H-bridge, high-side or low-side driver. The half-bridge outputs of the device are intended to drive motor or LEDs loads. The half-bridge drivers can be programmed to drive loads continuously (without PWM) or in chopping mode (with PWM) and in parallel operation for driving high current.

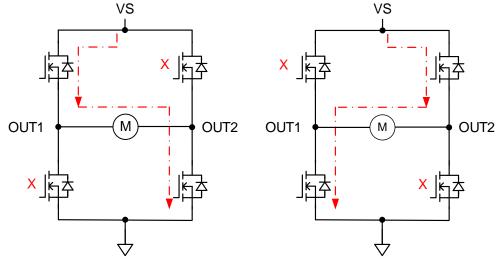

#### Continuous Mode (Without PWM)

The half-bridge drivers can be programmed to drive loads continuously (without PWM). The device can set the high-side enable bits (HBx\_HS\_EN) and low-side enable bits (HBx\_LS\_EN) in operation control registers (OP\_CTRL\_1, OP\_CTRL\_2) to turn on/off high-side or low-side MOSFETs individually. In addition, the device will stay in Hi-Z mode if high-side and low-side switch are set high of a half-bridge. An illustration is shown in Figure 4 and Figure 5, OUT1 and OUT2 driving a DC brush motor. With this configuration. The motor will work in forward direction with high-side FET of OUT1 and low-side FET of OUT2, and the motor current will flow from OUT1 into OUT2. Similarly, if turn on the high-side FET of OUT2 and low-side FET of OUT1, the motor will work in reverse, the motor current will flow from OUT2 into OUT2.

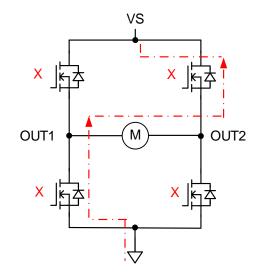

Figure 4. Continuous Mode (Forward)Figure 5. Continuous Mode (Reverse)If the motor initially running in forward or reverse direction, then switch high-side and low-side off, the H-bridge will<br/>operation in coast mode. Because of the inductance energy, the current will continue to flow in motor and take the path<br/>flow through the body diodes of FETs, shown in Figure 6 and Figure 7.

# SY2A58152

#### Figure 6. Coast-From Forward

Figure 7. Coast-From Reverse

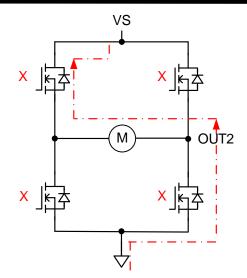

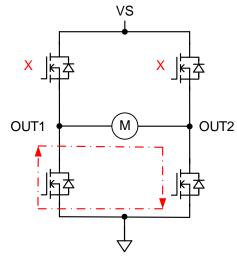

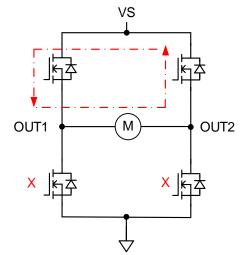

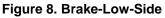

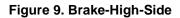

If the motor initially running in forward or reverse direction, then switch both high-side or low-side on, the H-bridge will operation in brake mode. For the low-side braking, both low-side FETs of the driver are turned on. Similarly, both high-side FETs of the driver are turned on for the high-side braking, shown in Figure 8 and Figure 9.

#### **Chopping Mode (With PWM)**

Each half-bridge can be configured into PWM mode to drive an inductive load (e.g., DC brush motor), and has been allocated four PWM channels with individual duty cycle settings with 8-bit resolution. The device has four PWM frequency 80-Hz, 100-Hz, 200-Hz and 2-kHz for different application.

The PWM chopping mode operation is configured in five steps as follows:

- 1. PWM Configuration

- 2. Free-wheeling Mode (Synchronous Rectification) Disable/Enable

- 3. PWM Channels Mapping

- 4. PWM Channels Configuration (PWM Frequency and PWM Duty)

- 5. Half-bridge Enable

#### **PWM Configuration**

Half-bridge can be configured into continuous mode or chopping mode (PWM mode) by using the PWM control register (PWM\_CTRL\_1 and PWM\_CTRL\_2). The HBx\_PWM bit = 1 is set to enable the PWM switching mode, otherwise it will operate in continuous mode. The PWM\_CHx\_DIS bit in PWM control register (PWM\_CTRL\_2) is set to enable the PWM generator.

#### Free-Wheeling Mode (Synchronous Rectification) Disable/Enable

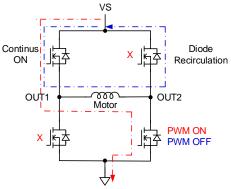

The device support to select the synchronous rectification mode by setting the HBx\_FW bit in free-wheeling control registers (FW\_CTRL\_1 and FW\_CTRL\_2). Figure 10 shows when the HBx\_FW is disable, the current path will go through the high-side diode during the PWM off time. If the HBx\_FW is enabled, it will open the FET to create a current path. Figure 11 shows example of the synchronous rectification, where the high-side FET of OUT2 half-bridge is turned on when the low-side FET of same half-bridge is turned off in a PWM cycle.

#### Figure 10. PWM Mode (Synchronous Rectification =OFF)

Figure 11. PWM Mode (Synchronous Rectification =ON)

#### **PWM Channels Mapping**

By configuring the PWM map control registers (PWM\_MAP\_CTRL\_x), the any of the OUTx half bridge outputs can map different PWM generator, because the device includes 4 PWM generators. The HBx\_PWM\_MAP bits are used to map any of the 12 channels, as shown in Table 1.

| Table 1. PWM Mapping |                             |  |  |  |  |  |  |

|----------------------|-----------------------------|--|--|--|--|--|--|

| HBx_PWM MAP BITS     | PWM CHANNEL                 |  |  |  |  |  |  |

| HBx_PWM_MAP=00b      | Channel 1 selected for OUTx |  |  |  |  |  |  |

| HBx_PWM_MAP=01b      | Channel 2 selected for OUTx |  |  |  |  |  |  |

| HBx_PWM_MAP=10b      | Channel 3 selected for OUTx |  |  |  |  |  |  |

| HBx_PWM_MAP=11b      | Channel 4 selected for OUTx |  |  |  |  |  |  |

#### PWM Channels Configuration (PWM Frequency and PWM Duty)

Each PWM generator can be configured different frequency and duty independently. The PWM frequency of each channel is controlled by the PWM frequency control register (PWM\_FREQ\_CTRL). The PWM\_DUTY\_CHx bit of the PWM duty control register (PWM\_DUTY\_CTRL\_x) is used to control PWM duty output, detailed shown in Table 2.

| Table 2. PWM Frequency |             |  |  |  |  |  |

|------------------------|-------------|--|--|--|--|--|

| HBX_PWM MAP BITS       | PWM CHANNEL |  |  |  |  |  |

| PWM_CHx_FREQ=00b       | 80Hz        |  |  |  |  |  |

| PWM_CHx_FREQ =01b      | 100Hz       |  |  |  |  |  |

| PWM_CHx_FREQ =10b      | 200Hz       |  |  |  |  |  |

| PWM_CHx_FREQ =11b      | 2000Hz      |  |  |  |  |  |

#### Table 3. PWM Duty Control Channelx Register Field Descriptions

| Bit | Field        | Туре | Default  | Description                                                                                             |

|-----|--------------|------|----------|---------------------------------------------------------------------------------------------------------|

| 7-0 | PWM_DUTY_CHx | R/W  | 0000000b | 0000000b = 0 % PWM Duty<br>1111111b = 100 % PWM Duty<br>Calculate duty as decimal (xxxxxxxb) ×<br>1/255 |

#### Half-Bridge Enable

After the four steps, the last step is set high-side or low-side enable. Once the half-bridge is configured for the PWM generation, the half-bridge is enabled by enabling either of the high-side or low-side switch. The HBx\_HS\_EN bit is used to set the high-side enable, and the HBx\_LS\_EN bit is used to set the low-side enable in operation control registers (OP\_CTRL\_1, OP\_CTRL\_2, OP\_CTRL\_3).

#### **Protection Circuits**

This device has embedded protective functions such as undervoltage, overvoltage, overcurrent, power on reset, open load, thermal shutdown.

#### Undervoltage Lockout (UVLO)

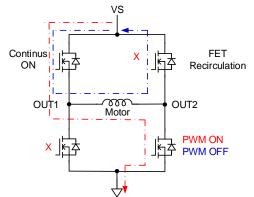

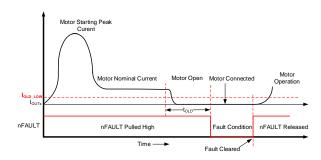

When voltage VS drops below  $V_{UVLO_FALL}$ , all output stages are switched off. However, the logic information remains intact and uncorrupted. The VS under-voltage error bit is also latched high in the IC status register (IC\_START), the nFAULT pin is driven low. If VS voltage rises again and reaches the switch on voltage  $V_{UVLO_RISE}$  threshold, the power stages will automatically be activated and the nFAULT pin is released. The UVLO error bit remains set until cleared through the CLR\_FLT bit.

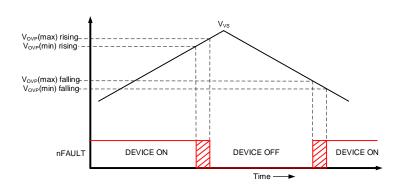

Figure 12. VS UVLO Operation

#### Overvoltage Protection (OVP)

In the event the supply voltage VS rises above the switch off voltage  $V_{OVP}$ , all output stages are switched off. The VS overvoltage error bit is also latched high in the IC status register (IC\_START), the nFAULT pin is driven low. If VS falls again and reaches the switch-on voltage threshold ( $V_{OVP}$  - $V_{OVP_-HYS}$ ), the power stages will automatically be activated and the nFAULT pin is released. The OVP error bit remains set until cleared through the CLR\_FLT bit. The device supports an extended overvoltage operation for higher over-voltage range up to 33V by enabling the EXT\_OVP bit in CONFIG\_CTRL register.

Figure 13. VS OVP Operation

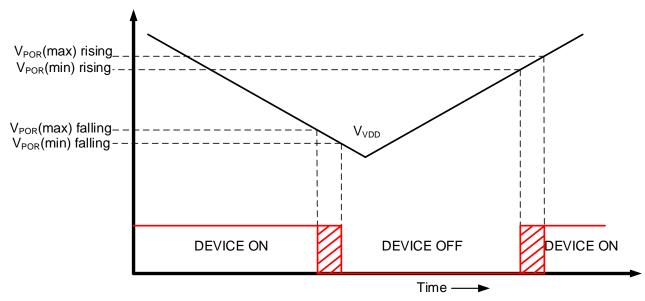

#### VDD Power on Reset (POR)

In the event the VDD logic supply decreases below the undervoltage threshold, V<sub>POR\_FALL</sub>, the SPI interfaces no longer be functional and the device will enter reset mode. The digital block will be initialized and the output stages are switched off to high impedance. The undervoltage reset is released once VDD voltage levels are above the undervoltage threshold, V<sub>POR\_ON</sub>. The reset event is reported in CONFIG\_CTRL register by the NPOR bit. The NPOR error bit remains reset and latched low until cleared through the CLR\_FLT bit.

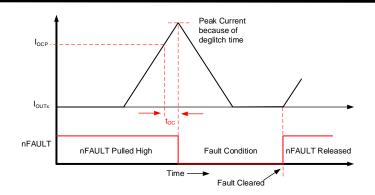

#### **Overcurrent Protection (OCP)**

The device offers over current protection. Monitoring the current on the high side and low side drivers at any time, once the current exceeds the overcurrent shutdown threshold, the corresponding HS or LS driver is latched off and the corresponding error bit, HBx\_HS\_OCP or HBx\_LS\_OCP is set and latched after the specified shutdown time, toc. To resume normal functionality of the power switch (in the event the overcurrent condition disappears or to verify if the failure still exists), user could disable the OCP fault on the nFAULT pin by setting the OCP\_REP bit in the CONFIG\_CTRL register.

Figure 15. Over Current Protection

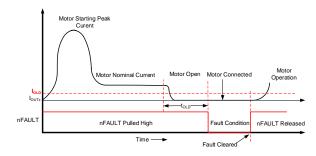

#### Open Load Detection (OLD)

The open-load detection (OLD) function ensures the proper load connection. The device support active OLD and low-current OLD.

#### Active OLD

Active OLD can identify an open-load condition on the OUTx pins while driving a load. As shown in Figure 16, open-load fault would be detected if the motor current  $I_{OUTx}$  is lower than the open-load current threshold ( $I_{OLD}$ ) and the duration of fault condition longer than the open-load deglitch time ( $t_{OLD}$ ). If the active OLD happen, the nFAULT pin will go down. When the open-load condition is removed and set the CLR\_FLT bit to 1, the nFAULT pin be released. The controller also can read the register to know whether there is an open-load condition. The OLD bit in the IC status (IC\_STAT) register will be set to 1 and HBx\_HS\_OLD or HBx\_LS\_OLD bit in the open-load status register (OLD\_STAT\_x) will be set to 1. There are two OLD control registers (OLD\_CTRL\_1 and OLD\_CTRL\_2) are used to configure OLD function. The HBx\_OLD\_DIS bit in OLD\_CTRL\_1 register allows the user to disable OLD on the OUTx pins, OLD on the devices is enabled by default. The OLD\_REP bit in the OLD\_CTRL\_2 register determines whether report on the nFAULT pin. The OLD\_OP bit determines the response of the device to an active OLD fault. If OLD\_OP = 0, the OUTx pins go to the Hi-Z state to stop driving the outputs. Otherwise, the OUTx pins will stay in their previous state and do not react to the OLD fault unless the controller takes action.

#### Low-Current OLD

The device also includes a low-current OLD mode which is similar with active open-load detection. The difference between low-current open-load and active open-load is the current detection threshold. The current detection threshold is around 10x lower than the active open-load detection scheme. In addition, the low-current open-load only work in the low-side MOSFET. Enable the low-current OLD mode will also disable the high-side OLD for the particular half-bridge. As shown in Figure 17, If the motor current  $I_{OUTx}$  is lower than the open-load current threshold ( $I_{OLD\_LOW}$ ) and the duration of fault condition longer than the open-load deglitch time ( $t_{OLD}$ ). The device will identify a low-current open-load fault condition. If the low-current OLD happen, the nFAULT pin will go down. When the open-load condition is removed and set the CLR\_FLT bit to 1, the nFAULT pin release. The controller also can read the register to know whether there is an open-load fault. The OLD bit in the IC status (IC\_STAT) register will be set to 1 and HBx\_LS\_OLD bit in the open-load status register (OLD STAT x) will be set to 1.

Figure 16. Active Open-load Detection

Figure 17. Low-current OLD

#### **Thermal Warning (OTW)**

The device offers temperature warning protection. If one or more temperature sensors reach the warning temperature, the temperature pre-warning bit, OTW is set in the IC status (IC\_START) register. This bit is latched and can only be cleared via SPI, but the outputs stages remain activated. The reporting of OTW on the nFAULT pin can be enabled by setting the over-temperature warning reporting (OTW\_REP) bit in the configuration control (CONFIG\_CTRL) register. The nFAULT pin releases when the die temperature decreases below the hysteresis point of the thermal warning (T<sub>WARN\_HYS</sub>)

#### Thermal Shutdown (TSD)

If one or more temperature sensors reach the shut-down temperature threshold, all outputs are latched off and the nFAULT pin is driven low. The OTSD bit is set in the IC status (IC\_START) register. All outputs will be activated and the nFAULT pin is released when the overtemperature shutdown condition is removed and die temperature decreases below the hysteresis point of the thermal warning ( $T_{HYS}$ ). The OTSD bit remains latched high indicating that a thermal event occurred until a clear fault command is issued through the CLR\_FLT bit. This protection feature cannot be disabled.

#### **Programming Configuration**

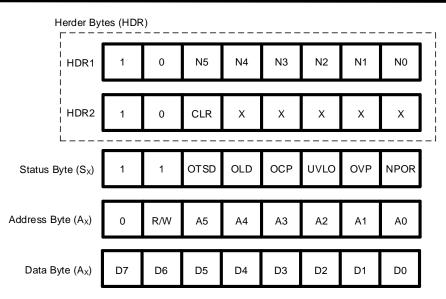

#### <u>SPI</u>

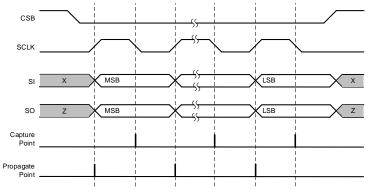

The device supports standard 16-bit SPI to be controlled. The commutation is performed by MSB clocked in first. The SPI interface is a synchronous serial interface for address and data transfer at bit rates of up to 5MHz. It is configured in 8-bit bytes designed to interface with a standard SPI bus. Four pins are used to communicate on the SPI: SCLK (synchronous clock), CSB (chip select, active low), SI (data input to the device for write operations,) and SO (data output from the device for read operations). As shown in Figure 18.

#### Figure 18. SPI Data Frame

A valid frame must meet the following conditions:

1). When the CSB pin is pulled high, any signals at the SCLK and SI pins are ignored and the SO pin is placed in the Hi-Z state

- 2). Data is captured on the falling edge of SCLK and data is propagated on the rising edge of SCLK

- 3). The most significant bit (MSB) is shifted in and out first

- 4). A full 16 SCLK cycles must occur for transaction to be valid

- 5). Data word sent to the SI pin should not be less than or more than 16 bits

6). For a write command, the existing data in the register being written to is shifted out on the SO pin following the 8-bit command data

#### SPI Format

Each SPI communication starts with one address byte followed by one data byte. The SPI function of the device has 1 R/W bit in bit14, 6 address bits and 8 data bits. The control registers are READ/WRITE registers. To set the control register to READ, bit 14 of the address must be programmed to '1', otherwise '0' for WRITE. While the microcontroller sends the address byte on SI, SO shifts out the IC Status Register data. A further data byte (bit7-bit0) is allocated to either configure the half-bridges or retrieve status information of the device. The SPI Registers have been mapped as shown in Table 6 respectively.

|          |     | R/W |     | Address |     |     |    |    | ddress Data |    |    |    |    |    |    |    |

|----------|-----|-----|-----|---------|-----|-----|----|----|-------------|----|----|----|----|----|----|----|

| Bit      | B15 | B14 | B13 | B12     | B11 | B10 | B9 | B8 | B7          | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

| Dat<br>a | 0   | W0  | A5  | A4      | A3  | A2  | A1 | A0 | D7          | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

Table / Sl Input Data Word Format

| Table 5 | SO Output | Data Word | Format |

|---------|-----------|-----------|--------|

|          |     |     |      | Address |     |      |         |      | Data |    |    |    |    |    |    |    |

|----------|-----|-----|------|---------|-----|------|---------|------|------|----|----|----|----|----|----|----|

| Bit      | B15 | B14 | B13  | B12     | B11 | B10  | B9      | B8   | B7   | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

| Dat<br>a | 1   | 1   | OTSD | OLD     | OCP | UVLO | OV<br>P | NPOR | D7   | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

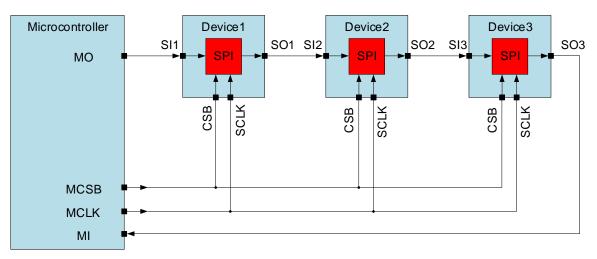

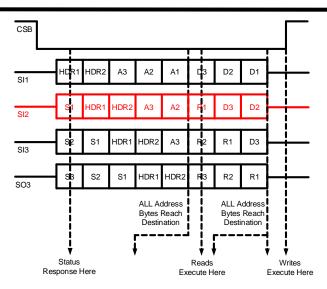

#### <u>Daisy Chain</u>

The device supports daisy chain operation with devices with the same SPI protocol shown in Figure 20. The master output (MO) is connected to a slave SI and the first slave SO is connected to the next slave SI to form a chain. The SO of the final slave in the chain will be connected to the master input (MI) to close the loop of the SPI communication frame. In daisy chain configuration, a single chip selects, CSB, and clock signal, SCLK, connected in parallel to each slave device, are used by the microcontroller to control or access the SPI devices. Figure 19 shows the topology when 3 devices are connected in series with waveforms.

#### Figure 19. SPI Daisy Chain

#### Figure 20. Daisy Chain SPI Operation

The first device in the chain shown above receives data from the master controller in the following format. See SI1 in Figure 20.

1). 2 bytes of Header

2). 3 bytes of Address

3). 3 bytes of Data

After the data has been transmitted through the chain, the master controller receives it in the following format. See SO3 in Figure 20.

1). 3 bytes of Status

2). 2 bytes of Header (should be identical to the information controller sent)

3). 3 bytes of Report

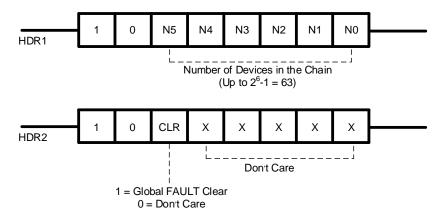

There are two Header bytes contain information of the number of devices and a global clear fault. The N5 to N0 in Header1 shows up to 2<sup>6</sup>-1 devices can be connected in series per daisy chain connection. The CLR bit in Header2 is a global clear fault command that will clear the fault registers of all the devices. Both two Header bytes must start with 1 and 0.

#### Figure 21. Header Bits

All the device will feedback fault status register in the status byte shown in Figure 21.It will be very convenient for the controller to read fault status and for the device to work efficiently.

#### Figure 22. Daisy Chain Read Registers

The device can count the number of Status bytes behind the Header byte to recognize its position. As shown in Figure 20, the device 2 has One Status bytes (S1) behind the Header byte and the device 3 has Two Status bytes (S1, S2) behind the Header byte. When the device knows its position and the number of devices connected in the chain, the device could load the relevant address and data byte in its buffer and bypasses the other bits. In this way, even the chain has 63 devices, the device still works fleetly.

| Table 6. | SY2A58152 | Register Map |

|----------|-----------|--------------|

|----------|-----------|--------------|

|                 |             |             |              |             | -                       | •            |              |             |      |         |

|-----------------|-------------|-------------|--------------|-------------|-------------------------|--------------|--------------|-------------|------|---------|

| Name            | 7           | 6           | 5            | 4           | 3                       | 2            | 1            | 0           | Type | Address |

| IC_STAT         | Reserved    | OTSD        | OTW          | OLD         | OCP                     | UVLO         | OVP          | NPOR        | R    | 00h     |

| OCP_STAT_1      | HB4_HS_OCP  | HB4_LS_OCP  | HB3_HS_OCP   | HB3_LS_OCP  | HB2_HS_OCP              | HB2_LS_OCP   | HB1_HS_OCP   | HB1_LS_OCP  | R    | 01h     |

| OCP_STAT_2      | HB8_HS_OCP  | HB8_LS_OCP  | HB7_HS_OCP   | HB7_LS_OCP  | HB6_HS_OCP              | HB6_LS_OCP   | HB5_HS_OCP   | HB5_LS_OCP  | R    | 02h     |

| OCP_STAT_3      | HB12_HS_OCP | HB12_LS_OCP | HB11_HS_OCP  | HB11_LS_OCP | HB10_HS_OCP             | HB10_LS_OCP  | HB9_HS_OCP   | HB9_LS_OCP  | R    | 03h     |

| OLD_STAT_1      | HB4_HS_OLD  | HB4_LS_OLD  | HB3_HS_OLD   | HB3_LS_OLD  | HB2_HS_OLD              | HB2_LS_OLD   | HB1_HS_OLD   | HB1_LS_OLD  | R    | 04h     |

| OLD_STAT_2      | HB8_HS_OLD  | HB8_LS_OLD  | HB7_HS_OLD   | HB7_LS_OLD  | HB6_HS_OLD              | HB6_LS_OLD   | HB5_HS_OLD   | HB5_LS_OLD  | R    | 05h     |

| OLD_STAT_3      | HB12_HS_OLD | HB12_LS_OLD | HB11_HS_OLD  | HB11_LS_OLD | HB10_HS_OLD             | HB10_LS_OLD  | HB9_HS_OLD   | HB9_LS_OLD  | R    | 06h     |

| CONFIG_CTRL     |             |             | erved        |             | OCP                     |              | EXT_OVP      | CLR_FLT     | RW   | 07h     |

| OP_CTRL_1       | HB4_HS_EN   | HB4_LS_EN   | HB3_HS_EN    | HB3_LS_EN   | HB2_HS_EN               | HB2_LS_EN    | HB1_HS_EN    | HB1_LS_EN   | RW   | 08h     |

| OP_CTRL_2       | HB8_HS_EN   | HB8_LS_EN   | HB7_HS_EN    | HB7_LS_EN   | HB6_HS_EN               | HB6_LS_EN    | HB5_HS_EN    | HB5_LS_EN   | RW   | 09h     |

| OP_CTRL_3       | HB12_HS_EN  | HB12_LS_EN  | HB11_HS_EN   | HB11_LS_EN  | HB10_HS_EN              | HB10_LS_EN   | HB9_HS_EN    | HB9_LS_EN   | RW   | 0Ah     |

| PWM_CTRL_1      | HB8_PWM     | HB7_PWM     | HB6_PWM      | HB5_PWM     | HB4_PWM                 | HB3_PWM      | HB2_PWM      | HB1_PWM     | RW   | 0Bh     |

| PWM_CTRL_2      | PWM_CH4_DIS | PWM_CH3_DIS | PWM_CH2_DIS  | PWM_CH1_DIS | HB12_PWM                | HB11_PWM     | HB10_PWM     | HB9_PWM     | RW   | 0Ch     |

| FW_CTRL_1       | HB8_FW      | HB7_FW      | HB6_FW       | HB5_FW      | HB4_FW                  | HB3_FW       | HB2_FW       | HB1_FW      | RW   | 0Dh     |

| FW_CTRL_2       |             | Rese        | erved        |             | HB12_FW                 | HB11_FW      | HB10_FW      | HB9_FW      | RW   | 0Eh     |

| PWM_MAP_CTRL_1  | HB4_PV      | VM_MAP      | HB3_PV       | /M_MAP      | HB2_PWM_MAP HB1_PWM_MAP |              |              |             |      | 0Fh     |

| PWM_MAP_CTRL_2  | HB8_PV      | VM_MAP      | HB7_PWM_MAP  |             | HB6_PWM_MAP             |              | HB5_PWM_MAP  |             | RW   | 10h     |

| PWM_MAP_CTRL_3  | HB12_P\     | NM_MAP      | HB11_PWM_MAP |             | HB10_PWM_MAP            |              | HB9_PWM_MAP  |             | RW   | 11h     |

| PWM_FREQ_CTRL   | PWM_CI      | H4_FREQ     | PWM_CH       | H3_FREQ     | PWM_CH                  | H2_FREQ      | PWM_CH       | RW          | 12h  |         |

| PWM_DUTY_CTRL_1 |             |             |              | PWM_I       | DUTY_CH1                |              |              |             |      | 13h     |

| PWM_DUTY_CTRL_2 |             |             |              | PWM_[       | DUTY CH2                |              |              |             |      | 14h     |

| PWM_DUTY_CTRL_3 |             |             |              | PWM_I       | DUTY_CH3                |              |              |             | RW   | 15h     |

| PWM_DUTY_CTRL_4 |             |             |              | PWM_I       | DUTY_CH4                |              |              |             | RW   | 16h     |

| SR_CTRL_1       | HB8_SR      | HB7_SR      | HB6_SR       | HB5_SR      | HB4_SR                  | HB3_SR       | HB2_SR       | HB1_SR      | RW   | 17h     |

| SR_CTRL_2       |             | Rese        | erved        |             | HB12_SR                 | HB11_SR      | HB10_SR      | HB9_SR      | RW   | 18h     |

| OLD_CTRL_1      | HB8_OLD_DIS | HB7_OLD_DIS | HB6_OLD_DIS  | HB5_OLD_DIS | HB4_OLD_DIS             | HB3_OLD_DIS  | HB2_OLD_DIS  | HB1_OLD_DIS | RW   | 19h     |

| OLD_CTRL_2      | OLD_REP     | OLD_OP      | Rese         |             | HB12_OLD_DIS            | HB11_OLD_DIS | HB10_OLD_DIS | HB9_OLD_DIS | RW   | 1Ah     |

| OLD_CTRL_3      |             | OCP_DEG     |              | Reserved    | HB12_LOLD_EN            | HB11_LOLD_EN | HB10_LOLD_EN | HB9_LOLD_EN | RW   | 1Bh     |

| OLD_CTRL_4      | HB8_LOLD_EN | HB7_LOLD_EN | HB6_LOLD_EN  | HB5_LOLD_EN | HB4_LOLD_EN             | HB3_LOLD_EN  | HB2_LOLD_EN  | HB1_LOLD_EN | RW   | 24h     |

|                 |             |             |              |             |                         |              |              |             |      |         |

#### **SPI Status Registers**

The Status Register are used to report warning and fault conditions. The status registers are read-only registers. **IC STAT**

#### IC\_Status Register (Address =0x00) [reset =0x00]

| D7       | D6   | D5  | D4  | D3  | D2   | D1  | D0   |

|----------|------|-----|-----|-----|------|-----|------|

| Reserved | OTSD | OTW | OLD | OCP | UVLO | OVP | NPOR |

| r        | r    | r   | r   | r   | r    | r   | r    |

| Field    | Bits | Туре | Description                                                                                                                                                                                                        |  |  |  |  |

|----------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Reserved | D7   | r    |                                                                                                                                                                                                                    |  |  |  |  |

| OTSD     | D6   | r    | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                               |  |  |  |  |

| OTW      | D5   | r    | Temperature pre-warning error detection<br>O <sub>B</sub> Junction temperature below temperature pre-warning<br>threshold<br>1 <sub>B</sub> Junction temperature has reached temperature pre-warning<br>threshold. |  |  |  |  |

| OLD      | D4   | r    | Open Load error detection<br>O <sub>B</sub> No Open Load<br>1 <sub>B</sub> Open load                                                                                                                               |  |  |  |  |

| OCP      | D3   | r    | Over current error detection<br>O <sub>B</sub> No Over current<br>1 <sub>B</sub> Over current                                                                                                                      |  |  |  |  |

| UVLO     | D2   | r    | VS Undervoltage error detection<br>$O_B$ No undervoltage on VS detected<br>$1_B$ Undervoltage on VS detected                                                                                                       |  |  |  |  |

| OVP      | D1   | r    | VS Overvoltage error detection<br>0 <sub>B</sub> No overvoltage on VS detected<br>1 <sub>B</sub> Overvoltage on VS detected                                                                                        |  |  |  |  |

| NPOR     | D0   | r    | Not Power on Reset (NPOR) detection<br>$0_B$ POR on EN or VDD supply rail<br>$1_B$ No POR                                                                                                                          |  |  |  |  |

#### OCP\_STAT\_1

#### Overcurrent Error Status of Half-bridge Outputs 1-4 (Address =0x01) [reset =0x00]

| D7        | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| HB4_HS_OC | HB4_LS_OC | HB3_HS_OC | HB3_LS_OC | HB2_HS_OC | HB2_LS_OC | HB1_HS_OC | HB1_LS_OC |

| r         | r         | r         | r         | r         | r         | r         | r         |

| Field     | Bits | Туре | Description                                                  |

|-----------|------|------|--------------------------------------------------------------|

|           |      |      | High-side (HS) switch of half-bridge 4 overcurrent detection |

| HB4_HS_OC | D7   | r    | 0 <sub>B</sub> No error on HS4 switch                        |

|           |      |      | 1 <sub>B</sub> Overcurrent detected on HS4 switch            |

|           |      |      | Low-side (LS) switch of half-bridge 4 overcurrent detection  |

| HB4_LS_OC | D6   | r    | 0 <sub>B</sub> No error on LS4 switch                        |

|           |      |      | 1 <sub>B</sub> Overcurrent detected on LS4 switch            |

|           |      |      | High-side (HS) switch of half-bridge 3 overcurrent detection |

| HB3_HS_OC | D5   | r    | 0 <sub>B</sub> No error on HS3 switch                        |

|           |      |      | 1 <sub>B</sub> Overcurrent detected on HS3 switch            |

|           |      |      | Low-side (LS) switch of half-bridge 3 overcurrent detection  |

| HB3_LS_OC | D4   | r    | 0 <sub>B</sub> No error on LS3 switch                        |

|           |      |      | 1 <sub>B</sub> Overcurrent detected on LS3 switch            |

| HB2_HS_OC | D3 | r | High-side (HS) switch of half-bridge 2 overcurrent detection $0_B$ No error on HS2 switch $1_B$ Overcurrent detected on HS2 switch |

|-----------|----|---|------------------------------------------------------------------------------------------------------------------------------------|

| HB2_LS_OC | D2 | r | Low-side (LS) switch of half-bridge 2 overcurrent detection $O_B$ No error on LS2 switch $1_B$ Overcurrent detected on LS2 switch  |

| HB1_HS_OC | D1 | r | High-side (HS) switch of half-bridge 1 overcurrent detection $O_B$ No error on HS1 switch $1_B$ Overcurrent detected on HS1 switch |

| HB1_LS_OC | D0 | r | Low-side (LS) switch of half-bridge 1 overcurrent detection $O_B$ No error on LS1 switch $1_B$ Overcurrent detected on LS1 switch  |

#### OCP\_STAT\_2 Overcurrent Error Status of Half-bridge Outputs 5-8 (Address =0x02) [reset =0x00]

| D7        | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| HB8_HS_OC | HB8_LS_OC | HB7_HS_OC | HB7_LS_OC | HB6_HS_OC | HB6_LS_OC | HB5_HS_OC | HB5_LS_OC |

| r         | r         | r         | r         | r         | r         | r         | r         |

| Field     | Bits | Туре | Description                                                  |

|-----------|------|------|--------------------------------------------------------------|

|           |      |      | High-side (HS) switch of half-bridge 8 overcurrent detection |

| HB8_HS_OC | D7   | r    | 0 <sub>B</sub> No error on HS8 switch                        |

|           |      |      | 1 <sub>B</sub> Overcurrent detected on HS8 switch            |

|           |      |      | Low-side (LS) switch of half-bridge 8 overcurrent detection  |

| HB8_LS_OC | D6   | r    | 0 <sub>B</sub> No error on LS8 switch                        |

|           |      |      | 1 <sub>B</sub> Overcurrent detected on LS8 switch            |

|           |      |      | High-side (HS) switch of half-bridge 7 overcurrent detection |

| HB7_HS_OC | D5   | r    | 0 <sub>B</sub> No error on HS7 switch                        |

|           |      |      | 1 <sub>B</sub> Overcurrent detected on HS7 switch            |

|           |      |      | Low-side (LS) switch of half-bridge 7 overcurrent detection  |

| HB7_LS_OC | D4   | r    | 0 <sub>B</sub> No error on LS7 switch                        |

|           |      |      | 1 <sub>B</sub> Overcurrent detected on LS7 switch            |

|           |      |      | High-side (HS) switch of half-bridge 6 overcurrent detection |

| HB6_HS_OC | D3   | r    | 0 <sub>B</sub> No error on HS6 switch                        |

|           |      |      | 1 <sub>B</sub> Overcurrent detected on HS6 switch            |

|           |      |      | Low-side (LS) switch of half-bridge 6 overcurrent detection  |

| HB6_LS_OC | D2   | r    | 0 <sub>B</sub> No error on LS6 switch                        |

|           |      |      | 1 <sub>B</sub> Overcurrent detected on LS6 switch            |

|           |      |      | High-side (HS) switch of half-bridge 5 overcurrent detection |

| HB5_HS_OC | D1   | r    | 0 <sub>B</sub> No error on HS5 switch                        |

|           |      |      | 1 <sub>B</sub> Overcurrent detected on HS5 switch            |

|           |      |      | Low-side (LS) switch of half-bridge 5 overcurrent detection  |

| HB5_LS_OC | D0   | r    | 0 <sub>B</sub> No error on LS5 switch                        |

|           |      |      | 1 <sub>B</sub> Overcurrent detected on LS5 switch            |

#### OCP\_STAT\_3 Overcurrent Error Status of Half-bridge Outputs 9-12 (Address =0x03) [reset =0x00]

| D7         | D6         | D5         | D4         | D3         | D2         | D1        | D0        |

|------------|------------|------------|------------|------------|------------|-----------|-----------|

| HB12_HS_OC | HB12_LS_OC | HB11_HS_OC | HB11_LS_OC | HB10_HS_OC | HB10_LS_OC | HB9_HS_OC | HB9_LS_OC |

| r          | r          | r          | r          | r          | r          | r         | r         |

| Field      | Bits | Туре | Description                                                   |

|------------|------|------|---------------------------------------------------------------|

|            |      |      | High-side (HS) switch of half-bridge 12 overcurrent detection |

| HB12_HS_OC | D7   | r    | 0 <sub>B</sub> No error on HS12 switch                        |

|            |      |      | 1 <sub>B</sub> Overcurrent detected on HS12 switch            |

| HB12_LS_OC | D6   | r    | Low-side (LS) switch of half-bridge 12 overcurrent detection  |

|            |      |      | 0 <sub>B</sub> No error on LS12 switch                        |

|------------|------|------|---------------------------------------------------------------|

|            |      |      | 1 <sub>B</sub> Overcurrent detected on LS12 switch            |

|            |      |      | High-side (HS) switch of half-bridge 11 overcurrent detection |

| HB11_HS_OC | D5   | r    | 0 <sub>B</sub> No error on HS11 switch                        |

|            |      |      | 1 <sub>B</sub> Overcurrent detected on HS11 switch            |

|            |      |      | Low-side (LS) switch of half-bridge 11 overcurrent detection  |

| HB11_LS_OC | C D4 | r    | 0 <sub>B</sub> No error on LS11 switch                        |

|            |      |      | 1 <sub>B</sub> Overcurrent detected on LS11 switch            |

|            | C D3 | D3 r | High-side (HS) switch of half-bridge 10 overcurrent detection |

| HB10_HS_OC |      |      | 0 <sub>B</sub> No error on HS10 switch                        |

|            |      |      | 1 <sub>B</sub> Overcurrent detected on HS10 switch            |

|            |      |      | Low-side (LS) switch of half-bridge 10 overcurrent detection  |

| HB10_LS_OC | D2   | r    | 0 <sub>B</sub> No error on LS10 switch                        |

|            |      |      | 1 <sub>B</sub> Overcurrent detected on LS10 switch            |

|            |      |      | High-side (HS) switch of half-bridge 9 overcurrent detection  |

| HB9_HS_OC  | D1   | r    | 0 <sub>B</sub> No error on HS9 switch                         |

|            |      |      | 1 <sub>B</sub> Overcurrent detected on HS9 switch             |

|            |      |      | Low-side (LS) switch of half-bridge 9 overcurrent detection   |

| HB9_LS_OC  | D0   | r    | 0 <sub>B</sub> No error on LS9 switch                         |

|            |      |      | 1 <sub>B</sub> Overcurrent detected on LS9 switch             |

### OLD\_STAT\_1

#### Open Load Error Status of Half-bridge Outputs 1-4 (Address =0x04) [reset =0x00]

| D7        | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| HB4_HS_OL | HB4_LS_OL | HB3_HS_OL | HB3_LS_OL | HB2_HS_OL | HB2_LS_OL | HB1_HS_OL | HB1_LS_OL |

| r         | r         | r         | r         | r         | r         | r         | r         |

| Field     | Bits           | Туре | Description                                                                                                                                                            |

|-----------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HB4_HS_OL | D7             | r    | High-side (HS) switch of half-bridge 4 open load detection $O_B$ No error on HS4 switch (default value) $1_B$ Open load detected on HS4 switch                         |

| HB4_LS_OL | D6             | r    | Low-side (LS) switch of half-bridge 4 open load detection<br>$O_B$ No error on LS4 switch (default value)<br>$1_B$ Open load detected on LS4 switch                    |

| HB3_HS_OL | HB3_HS_OL D5 r |      | High-side (HS) switch of half-bridge 3 open load detection $O_B$ No error on HS3 switch (default value) $1_B$ Open load detected on HS3 switch                         |

| HB3_LS_OL | D4             | r    | Low-side (LS) switch of half-bridge 3 open load detection<br>O <sub>B</sub> No error on LS3 switch (default value)<br>1 <sub>B</sub> Open load detected on LS3 switch  |

| HB2_HS_OL | D3             | r    | High-side (HS) switch of half-bridge 2 open load detection<br>O <sub>B</sub> No error on HS2 switch (default value)<br>1 <sub>B</sub> Open load detected on HS2 switch |

| HB2_LS_OL | D2             | r    | Low-side (LS) switch of half-bridge 2 open loadt detection<br>O <sub>B</sub> No error on LS2 switch (default value)<br>1 <sub>B</sub> Open load detected on LS2 switch |

| HB1_HS_OL | D1             | r    | High-side (HS) switch of half-bridge 1 open load detection<br>O <sub>B</sub> No error on HS1 switch (default value)<br>1 <sub>B</sub> Open load detected on HS1 switch |

| HB1_LS_OL | D0             | r    | Low-side (LS) switch of half-bridge 1 open load detection $O_B$ No error on LS1 switch (default value) $1_B$ Open load detected on LS1 switch                          |

### OLD\_STAT\_2 Open Load Error Status of Half-bridge Outputs 5-8 (Address =0x05) [reset =0x00]

| D7        | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| HB8_HS_OL | HB8_LS_OL | HB7_HS_OL | HB7_LS_OL | HB6_HS_OL | HB6_LS_OL | HB5_HS_OL | HB5_LS_OL |

| r         | r         | r         | r         | r         | r         | r         | r         |

| Field     | Bits | Туре | Description                                                |

|-----------|------|------|------------------------------------------------------------|

|           |      |      | High-side (HS) switch of half-bridge 8 open load detection |

| HB8_HS_OL | D7   | r    | 0 <sub>B</sub> No error on HS8 switch                      |

|           |      |      | 1 <sub>B</sub> Open load detected on HS8 switch            |

|           |      |      | Low-side (LS) switch of half-bridge 8 open load detection  |

| HB8_LS_OL | D6   | r    | 0 <sub>B</sub> No error on LS8 switch                      |

|           |      |      | 1 <sub>B</sub> Open load detected on LS8 switch            |

|           |      |      | High-side (HS) switch of half-bridge 7 open load detection |

| HB7_HS_OL | D5   | r    | 0 <sub>B</sub> No error on HS7 switch                      |

|           |      |      | 1 <sub>B</sub> Open load detected on HS7 switch            |

|           |      |      | Low-side (LS) switch of half-bridge 7 open load detection  |

| HB7_LS_OL | D4   | r    | OB No error on LS7 switch                                  |

|           |      |      | 1 <sub>B</sub> Open load detected on LS7 switch            |

|           |      |      | High-side (HS) switch of half-bridge 6 open load detection |

| HB6_HS_OL | D3   | r    | 0 <sub>B</sub> No error on HS6 switch                      |

|           |      |      | 1 <sub>B</sub> Open load detected on HS6 switch            |

|           |      |      | Low-side (LS) switch of half-bridge 6 open load detection  |

| HB6_LS_OL | D2   | r    | 0 <sub>B</sub> No error on LS6 switch                      |

|           |      |      | 1 <sub>B</sub> Open load detected on LS6 switch            |

|           |      |      | High-side (HS) switch of half-bridge 5 open load detection |

| HB5_HS_OL | D1   | r    | 0 <sub>B</sub> No error on HS5 switch                      |

|           |      |      | 1 <sub>B</sub> Open load detected on HS5 switch            |

|           |      |      | Low-side (LS) switch of half-bridge 5 open load detection  |

| HB5_LS_OL | D0   | r    | 0 <sub>B</sub> No error on LS5 switch                      |

|           |      |      | 1 <sub>B</sub> Open load detected on LS5 switch            |

#### OLD\_STAT\_3 Open Load Error Status of Half-bridge Outputs 9-12 (Address =0x06) [reset =0x00]

| D7         | D6         | D5         | D4         | D3         | D2         | D1        | D0        |

|------------|------------|------------|------------|------------|------------|-----------|-----------|

| HB12_HS_OL | HB12_LS_OL | HB11_HS_OL | HB11_LS_OL | HB10_HS_OL | HB10_LS_OL | HB9_HS_OL | HB9_LS_OL |

| r          | r          | r          | r          | r          | r          | r         | r         |

| Field      | Bits | Туре | Description                                                 |

|------------|------|------|-------------------------------------------------------------|

|            |      |      | High-side (HS) switch of half-bridge 12 open load detection |

| HB12_HS_OL | D7   | r    | 0 <sub>B</sub> No error on HS12 switch                      |

|            |      |      | 1 <sub>B</sub> Open load detected on HS12 switch            |

|            |      |      | Low-side (LS) switch of half-bridge 12 open load detection  |

| HB12_LS_OL | D6   | r    | 0 <sub>B</sub> No error on LS12 switch                      |

|            |      |      | 1 <sub>B</sub> Open load detected on LS12 switch            |

|            |      |      | High-side (HS) switch of half-bridge 11 open load detection |

| HB11_HS_OL | D5   | r    | 0 <sub>B</sub> No error on HS11 switch                      |

|            |      |      | 1 <sub>B</sub> Open load detected on HS11 switch            |

|            |      |      | Low-side (LS) switch of half-bridge 11 open load detection  |

| HB11_LS_OL | D4   | r    | 0 <sub>B</sub> No error on LS11 switch                      |

|            |      |      | 1 <sub>B</sub> Open load detected on LS11 switch            |

|            |      |      | High-side (HS) switch of half-bridge 10 open load detection |

| HB10_HS_OL | D3   | r    | 0 <sub>B</sub> No error on HS10 switch                      |

|            |      |      | 1 <sub>B</sub> Open load detected on HS10 switch            |

|            | D2   | r    | Low-side (LS) switch of half-bridge 10 open load detection  |

| HB10_LS_OL | DZ   | I    | 0 <sub>B</sub> No error on LS10 switch                      |

|           |    |   | 1 <sub>B</sub> Open load detected on LS10 switch           |

|-----------|----|---|------------------------------------------------------------|

|           |    |   | High-side (HS) switch of half-bridge 9 open load detection |

| HB9_HS_OL | D1 | r | 0 <sub>B</sub> No error on HS9 switch                      |

|           |    |   | 1 <sub>B</sub> Open load detected on HS9 switch            |

|           |    |   | Low-side (LS) switch of half-bridge 9 open load detection  |

| HB9_LS_OL | D0 | r | 0 <sub>B</sub> No error on LS9 switch                      |

|           |    |   | 1 <sub>B</sub> Open load detected on LS9 switch            |

#### **SPI Control Registers**

The Control Register are used to configure the device. The control registers are read and write capable. **CONFIG\_CTRL**

#### Configuration Register (Address =0x07) [reset =0x00]

| D7       | D6       | D5       | D4       | D3      | D2      | D1      | D0      |

|----------|----------|----------|----------|---------|---------|---------|---------|

| Reserved | Reserved | Reserved | Reserved | OCP_REG | OTW_REG | EXT_OVP | CLR_FLT |

| r/w      | r/w      | r/w      | r/w      | r/w     | r/w     | r/w     | r/w     |

| Field    | Bits       | Туре | Description                                                                |

|----------|------------|------|----------------------------------------------------------------------------|

| Reserved | D7         | r/w  | Bit reserved. Always reads '0'.                                            |

| Reserved | D6         | r/w  | Bit reserved. Always reads '0'.                                            |

| Reserved | D5         | r/w  | Bit reserved. Always reads '0'.                                            |

| Reserved | D4         | r/w  | Bit reserved. Always reads '0'.                                            |

| OCP REG  | G D3       | r/w  | 0 <sub>B</sub> Overcurrent condition is reported in nFAULT pin             |

| OCF_REG  |            |      | 1 <sub>B</sub> Overcurrent condition warning is not reported in nFAULT pin |

| OTW REG  | <b>D</b> 2 | r/w  | 0 <sub>B</sub> Overtemperature warning is not reported in nFAULT pin       |

| UIW_REG  | D2         |      | 1 <sub>B</sub> Overtemperature warning is reported in nFAULT pin           |

| EXT OVP  | D1         | r/w  | 0 <sub>B</sub> Overvoltage protection threshold is at 21V min.             |

| EXI_OVP  | DI         |      | 1 <sub>B</sub> Overvoltage protection threshold is at 32.7V min.           |

|          | DO         | r/w  | OB Faults not cleared                                                      |

| CLR_FLT  | D0         |      | 1 <sub>B</sub> Clear all faults                                            |

#### OP\_CTRL\_1

#### Half-bridge Output Control 1(Address =0x08) [reset =0x00]

| D7        | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| HB4_HS_EN | HB4_LS_EN | HB3_HS_EN | HB3_LS_EN | HB2_HS_EN | HB2_LS_EN | HB1_HS_EN | HB1_LS_EN |

| r/w       |

| Field     | Bits | Туре | Description                                  |  |

|-----------|------|------|----------------------------------------------|--|

|           |      |      | Half-bridge output 4 High side switch enable |  |

| HB4_HS_EN | D7   | r/w  | 0 <sub>B</sub> HS4 OFF                       |  |

|           |      |      | 1 <sub>B</sub> HS4 ON                        |  |

|           |      |      | Half-bridge output 4 Low side switch enable  |  |

| HB4_LS_EN | D6   | r/w  | 0 <sub>B</sub> LS4 OFF                       |  |

|           |      |      | 1 <sub>B</sub> LS4 ON                        |  |

|           |      |      | Half-bridge output 3 High side switch enable |  |

| HB3_HS_EN | D5   | r/w  | 0 <sub>B</sub> HS3 OFF                       |  |

|           |      |      | 1 <sub>B</sub> HS3 ON                        |  |

|           |      |      | Half-bridge output 3 Low side switch enable  |  |

| HB3_LS_EN | D4   | r/w  | 0 <sub>B</sub> LS3 OFF                       |  |

|           |      |      | 1 <sub>B</sub> LS3 ON                        |  |

|           |      |      | Half-bridge output 2 High side switch enable |  |