# SY20797C

# **High Efficiency Switched Capacitor Charger**

# **General Description**

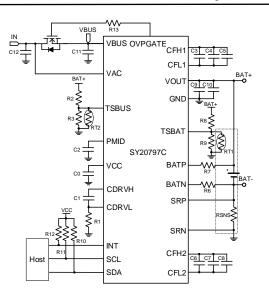

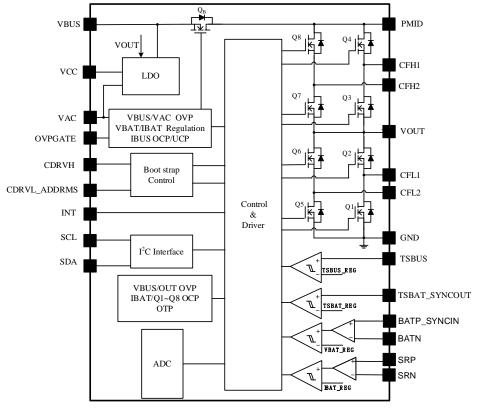

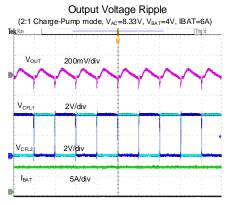

The SY20797C is a high efficiency switched capacitor charger for high power fast charging applications. As a voltage divider or a current doubler with 50% switching duty cycle, the SY20797C integrates extremely low  $R_{DS(ON)}$  MOSFETs and achieves up to 96.8% efficiency when  $V_{BAT} = 4V$  and  $I_{BAT} = 6A$ . It also provides a 9-channel, 12-bit ADC to monitor input and output voltage, current, and temperature for battery charging management by a host.

The SY20797C offers protection against multiple conditions, including external OVP-FET shutdown for input overvoltage protection, input overcurrent protection, output overvoltage and overcurrent protection, and temperature sensing for VBUS, battery, and die.

# **Applications**

- Smartphones/Tablets

- Other Handhelds

#### High Absolute Maximum Rating of 20V (V<sub>BUS</sub>)

- Battery Voltage Regulation (VBAT REG)

- Battery Current Regulation (IBAT REG)

- Integrated Input-Side NFET to Block Reverse Current

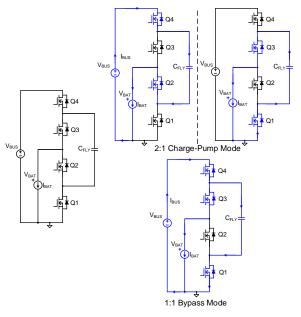

- Dual-Phase Switched Capacitor Converter

- 8A Output Current Capability

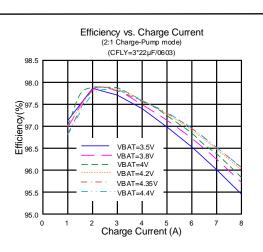

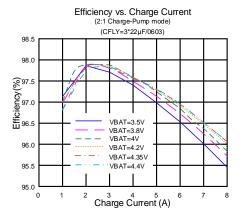

- Efficiency up to 96.8% when  $V_{BAT} = 4V$ ,  $I_{BAT} = 6A$

- Programmable Frequency

- Spread spectrum for improved EMI

- 2:1 Charge-pump Mode and 1:1 Bypass Mode

- Fully Integrated Power MOSFETs with Extremely Low R<sub>DS(ON)</sub>

- 50% Duty Cycle in 2:1 Charge-pump Mode

- Voltage Divider: Input Voltage = Output Voltage × 2

- Current Doubler: Output Current = Input Current × 2

- Soft-Start for Inrush Current Limit

- 9-Channel 12-Bit ADC

- V<sub>AC</sub>, V<sub>BUS</sub>, V<sub>OUT</sub>, V<sub>BAT</sub>

- IBUS, IBAT

- TSBUS, TSBAT, TDIE

- I<sup>2</sup>C Interface

### Features

• External OVP Control and Regulation

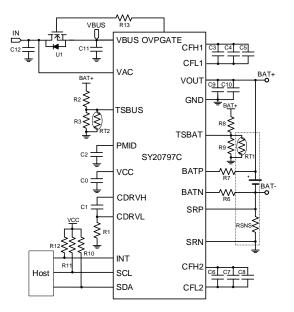

Figure 1. Typical Application Circuit

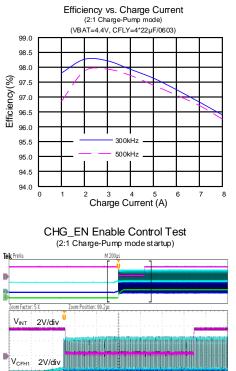

Figure 2. Efficiency vs. Output Current

# **Ordering Information**

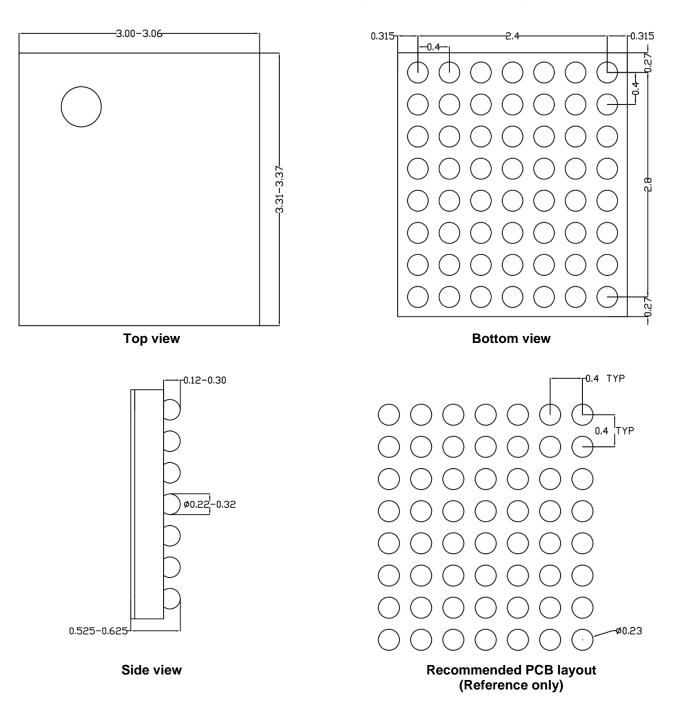

| Part Number | Package Type                                          | Top Mark       |

|-------------|-------------------------------------------------------|----------------|

| SY20797CVLS | CSP3.03×3.34-56<br>RoHS-Compliant and<br>Halogen-Free | EBN <i>xyz</i> |

x = year code, y = week code, z = lot number code

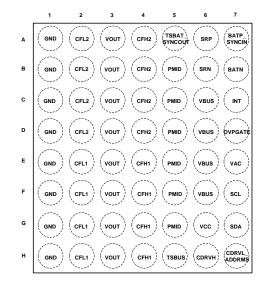

# Pinout (top view)

# **Pin Description**

| Pin No                     | Pin Name          | Description                                                                                                                                                                                                                                     |

|----------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1,B1,C1,D1<br>E1,F1,G1,H1 | GND               | Ground pin.                                                                                                                                                                                                                                     |

| A2,B2,C2,D2                | CFL2              | Low side switching node of switched capacitor converter.                                                                                                                                                                                        |

| E2,F2,G2,H2                | CFL1              | Low side switching node of switched capacitor converter.                                                                                                                                                                                        |

| A3,B3,C3,D3<br>E3,F3,G3,H3 | VOUT              | Switched capacitor converter output pin. Connect two 10µF capacitors to GND.                                                                                                                                                                    |

| A4,B4,C4,D4                | CFH2              | High side switching node of switched capacitor converter.                                                                                                                                                                                       |

| E4,F4,G4,H4                | CFH1              | High side switching node of switched capacitor converter.                                                                                                                                                                                       |

| A5                         | TSBAT_<br>SYNCOUT | Threshold detector input pin for battery temperature sensing. If the SY20797C is configured as a controller, this pin should be connected to BATP_SYNCIN of the peripheral device.                                                              |

| B5,C5,D5<br>E5,F5,G5       | PMID              | Input pin to switched capacitor converter. Connect a 10µF capacitor to GND.                                                                                                                                                                     |

| H5                         | TSBUS             | Threshold detector input pin for bus temperature sensing.                                                                                                                                                                                       |

| A6                         | SRP               | Positive input for battery current sensing. Place a sense resistor between SRP and SRN.                                                                                                                                                         |

| B6                         | SRN               | Negative input for battery current sensing. Place a sense resistor between SRP and SRN.                                                                                                                                                         |

| C6,D6,E6,F6                | VBUS              | Device power input pin.                                                                                                                                                                                                                         |

| G6                         | VCC               | Internal LDO output pin. Connect a 4.7µF MLCC capacitor to ground.                                                                                                                                                                              |

| H6                         | CDRVH             | High side switching node of internal charge pump for gate drive. Place a 220nF capacitor between CDRVH and CDRVL_ADDRMS.                                                                                                                        |

| A7                         | BATP_SYNCIN       | Positive input for battery voltage sensing. Connect a $100\Omega$ resistor to the positive terminal of the battery pack. If the SY20797C is configured as a peripheral, this pin should be connected to TSBAT_SYNCOUT of the controller device. |

| B7 | BATN            | Negative input for battery voltage sensing. Place a $100\Omega$ resistor to the negative terminal of the battery pack.                                                                                 |

|----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C7 | INT             | Open-drain, active-low interrupt output pin. Connect a $10k\Omega$ resistor to pullup voltage. This pin will be pulled low for 256µs if a fault or alarm occurs.                                       |

| D7 | OVPGATE         | External FET control pin. Connect to FET gate.                                                                                                                                                         |

| E7 | VAC             | Input voltage sense pin. Connect to external FET drain.                                                                                                                                                |

| F7 | SCL             | I <sup>2</sup> C Interface clock pin.                                                                                                                                                                  |

| G7 | SDA             | I <sup>2</sup> C Interface data pin.                                                                                                                                                                   |

| H7 | CDRL_<br>ADDRMS | Low side switching node of internal charge pump for gate drive. Place a 220nF capacitor between CDRVH and CDRVL_ADDRMS.<br>Also connect a resistor to ground to assign the address and mode of device. |

# **Block Diagram**

Figure 3. Block Diagram

# **Absolute Maximum Ratings**

| Parameter (Note 1)                                      | Min  | Max  | Unit |

|---------------------------------------------------------|------|------|------|

| VAC                                                     | -0.3 | 36   |      |

| VBUS, PMID, CDRVH                                       | -0.3 | 20   |      |

| CFH1- CFL1, CFH2-CFL2, VOUT, TSBUS, TSBAT_SYNCOUT, BATP | -0.3 | 7    | V    |

| OVPGATE-VBUS                                            | -0.3 | 10.8 |      |

| VCC, SRP-SRN, INT, SCL, SDA, BATN, CDRVL_ADDRMS         | -0.3 | 3.6  |      |

| Junction Temperature, Operating                         | -40  | 150  |      |

| Lead Temperature (Soldering, 10s)                       |      | 260  | °C   |

| Storage Temperature                                     | -65  | 150  |      |

# **Thermal Information**

| Parameter (Note 2)                                     | Тур  | Unit |

|--------------------------------------------------------|------|------|

| θ <sub>JA</sub> Junction-to-Ambient Thermal Resistance | 29   | °C/W |

| θ <sub>JC</sub> Junction-to-Case Thermal Resistance    | 5.5  | C/VV |

| $P_D$ Power Dissipation $T_A = 25^{\circ}C$            | 3.45 | W    |

# **Recommended Operating Conditions**

| Parameter (Note 3)                                      | Min  | Max | Unit |

|---------------------------------------------------------|------|-----|------|

| VAC                                                     | -0.3 | 12  |      |

| VBUS, PMID, CDRVH                                       | -0.3 | 12  |      |

| CFH1- CFL1, CFH2-CFL2, VOUT, TSBUS, TSBAT_SYNCOUT, BATP | -0.3 | 6   | V    |

| OVPGATE-VBUS                                            | -0.3 | 9.9 |      |

| VCC, SRP-SRN, INT, SCL, SDA, BATN, CDRVL_ADDRMS         | -0.3 | 3.3 |      |

# **Electrical Characteristics**

$(T_{A=}25^{\circ}C, unless otherwise specified.)$

| Parameter                  |                                | Symbol              | Test Conditions                                                                                                                                                         | Min  | Тур  | Max  | Unit |

|----------------------------|--------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| VAC Insert Threshold       |                                | Vac_insert          | VAC rising threshold to turn on<br>external FET                                                                                                                         |      |      | 3.2  | V    |

|                            |                                | Vac_hys             | Falling hysteresis                                                                                                                                                      | 200  | 300  | 400  | mV   |

|                            | VAC UVLO                       | Vac_uvlo            | Rising threshold                                                                                                                                                        | 2.5  | 2.7  | 2.9  | V    |

|                            |                                | VAC_UVLOHYS         | Falling hysteresis                                                                                                                                                      | 100  | 200  | 300  | mV   |

|                            | VBUS UVLO                      | VBUS_UVLO           | Rising threshold                                                                                                                                                        | 2.4  | 2.55 | 2.7  | V    |

|                            | 1003 0120                      | VBUS_HYS            | Falling hysteresis                                                                                                                                                      | 80   | 150  | 220  | mV   |

| Daviar                     |                                | Vout_uvlo           | Rising threshold                                                                                                                                                        | 2.4  | 2.55 | 2.7  | V    |

| Power<br>Supply            | VOUT UVLO                      | Vout_hys            | Falling hysteresis                                                                                                                                                      | 80   | 150  | 220  | mV   |

|                            | LDO Output Voltage             | Vcc                 | $V_{BUS} = 8V$ , $I_{VCC} = 0-30mA$                                                                                                                                     | 3.37 | 3.42 | 3.47 | V    |

|                            |                                |                     | ADC disable, charge disable,<br>OVPGATE not used                                                                                                                        | 0.75 | 1.1  | 1.4  | mA   |

|                            | VBUS Quiescent<br>Current      | Iq_vbus             | ADC disable, charge disable,<br>OVPGATE used                                                                                                                            |      | 1.5  |      | mA   |

|                            |                                |                     | ADC enable, charge disable,<br>OVPGATE not used                                                                                                                         |      | 1.2  | 1.5  | mA   |

|                            | VBAT Quiescent<br>Current      | I <sub>Q_VBAT</sub> | ADC disable, charge disable, VBUS not present                                                                                                                           |      | 10   | 20   | μA   |

|                            |                                |                     | ADC enable, charge disable                                                                                                                                              |      | 650  | 900  | μA   |

|                            | External FET Driver<br>Voltage | Vdrv                | OVPGATE-VBUS                                                                                                                                                            | 8.4  | 9    | 9.5  | V    |

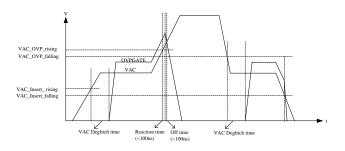

|                            | Turn-On FET Deglitch<br>Time   | VAC_FETDEG          | Deglitch time between triggering<br>V <sub>AC_INSERT</sub> and turning on FET                                                                                           | 18   | 20   | 22   | ms   |

|                            | VAC Present Deglitch<br>Time   | Vac_intdeg          | Deglitch time between triggering<br>V <sub>AC_INSERT</sub> and sending INT                                                                                              | 0.8  | 1    | 1.2  | ms   |

|                            | FET Turn-Off Time              | TFETOFF             |                                                                                                                                                                         |      | 100  |      | ns   |

|                            | FET Turn-Off<br>Reaction Time  | TREACTION           | Delay time between VAC OVP and<br>FET shutdown                                                                                                                          |      | 100  |      | ns   |

| External<br>OVP<br>Control | VBAT Regulation<br>Accuracy    | Vbat_regacc         | The threshold below VBAT_OVP<br>where the device starts regulation,<br>It is set by bit[5:4] of register 0x2C,<br>with the range 50mV to 200mV and<br>the step 50mV.    | -20  |      | 20   | mV   |

|                            | IBAT Regulation<br>Accuracy    | IBAT_REGACC         | The threshold below IBAT_OCP<br>where the device starts regulation,<br>It is set by bits[7:6] of register<br>0x2C, with the range 200mA to<br>500mA and the step 100mA. | -200 |      | 200  | mA   |

|                            | Regulation Timeout             | Ттімеоцт            | Maximum regulation time. If the time expires, the device will not charge.                                                                                               | 585  | 650  | 715  | ms   |

| MOSFET                     | On-Resistance                  | Rds(ON)             | Q <sub>B</sub>                                                                                                                                                          |      | 10   |      | mΩ   |

| NOOFET                     |                                | I VDS(UN)           | Q1,Q2,Q3,Q5,Q6,Q7                                                                                                                                                       |      | 7    |      | mΩ   |

| Parameter                    |                                     | Symbol                    | Test Conditions                                                                                                | Min  | Тур | Max  | Unit |

|------------------------------|-------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------|------|-----|------|------|

|                              |                                     |                           | Q4,Q8                                                                                                          |      | 15  |      | mΩ   |

|                              |                                     |                           | Register0x0B, bit[6:4] = '101'                                                                                 | 675  | 750 | 825  | kHz  |

| Frequency<br>and Duty        | Frequency                           | f <sub>SW</sub>           | Register0x0B, bit[6:4] = '100'                                                                                 | 450  | 500 | 550  | kHz  |

|                              |                                     |                           | Register0x0B, bit[6:4] = '010'                                                                                 | 270  | 300 | 330  | kHz  |

|                              | Duty-Cycle of Switch<br>Node Output | D <sub>sw</sub>           |                                                                                                                |      | 50  |      | %    |

|                              | Device Startup Time                 | tvccsart                  | Device startup time from internal<br>VDD > UVLO to I <sup>2</sup> C communication                              |      |     | 64   | ms   |

|                              | Soft-Start Time                     | <b>t</b> softsart         | Soft-start time from CHG_EN = 1 to<br>converter switching                                                      |      |     | 150  | ms   |

|                              | IBUS UCP Timeout<br>Accuracy        | tibus_ucp_<br>TIMEOUT_ACC | Register 0x2B bit[7:5], range:<br>12.5ms–100s                                                                  | -10  |     | 10   | %    |

| Internal<br>Timer            |                                     |                           | Register 0x0B bit[1:0] = '00'                                                                                  | 0.45 | 0.5 | 0.55 | S    |

| Timer                        | Watchdog Timeout                    | trucour                   | Register 0x0B bit[1:0] = '01'                                                                                  | 0.9  | 1   | 1.1  | S    |

|                              |                                     | <b>t</b> тімеоuт          | Register 0x0B bit[1:0] = '10'                                                                                  | 4.5  | 5   | 5.5  | S    |

|                              |                                     |                           | Register 0x0B bit[1:0] = '11'                                                                                  | 27   | 30  | 33   | s    |

|                              | INT Duration Time                   | t <sub>INT</sub>          | INT pulled low time when an event occurs                                                                       |      | 256 |      | μs   |

|                              | VAC OVP Accuracy                    | VAC_OVP_ACC               | Register 0x05 bit[2:0],<br>range: 11V–17V, step:1V                                                             | -2   |     | 2    | %    |

|                              | VAC OVP Hysteresis                  | V <sub>AC_OVP_HYS</sub>   |                                                                                                                |      | 500 |      | mV   |

|                              | VBUS OVP Accuracy                   | VBUS_OVP_ACC              | Register 0x06 bit[6:0],<br>range: 6V–12.35V, step:50mV<br>V <sub>BUS</sub> = 10V                               | -1   |     | 1    | %    |

|                              | VOUT OVP Accuracy                   | VOUT_OVP_ACC              |                                                                                                                | 4.8  | 4.9 | 5    | V    |

|                              | VBAT OVP Accuracy                   | VBAT_OVP_ACC              | Register 0x00 bit[5:0],<br>range: 3.5V–5.075V, step: 25mV<br>V <sub>BAT_OVP</sub> = 4.2V to 4.65V              | -1   |     | 1    | %    |

|                              |                                     |                           | Register 0x05 bit[4] = '0', default                                                                            | 245  | 300 | 355  | mV   |

| Protection                   | VDR OVP Accuracy                    | Vdr_ovp_acc               | Register 0x05 bit[4] = '1'                                                                                     | 345  | 400 | 455  | mV   |

| Threshold<br>and<br>Accuracy | IBUS OCP Accuracy                   | IBUS_OCP_ACC              | Register 0x08 bit[3:0],<br>range: 1A–4.75A, step: 250mA<br>I <sub>BUS_OCP</sub> = 2A                           | -10  |     | 10   | %    |

|                              |                                     |                           | I <sub>BUS_OCP</sub> = 4A                                                                                      | -5   |     | 5    | %    |

|                              | IBUS UCP_RISE                       | lawa waa                  | Register 0x2B bit[2] = '0'                                                                                     | 200  | 300 | 400  | mA   |

|                              | Accuracy                            | IBUS_UCP_RISE_ACC         | Register 0x2B bit[2] = '1'                                                                                     | 400  | 500 | 600  | mA   |

|                              | IBUS UCP_FALL                       |                           | Register 0x2B bit[2] = '0'                                                                                     | 10   | 150 | 290  | mA   |

|                              | Accuracy                            | BUS_UCP_FALL_ACC          | Register 0x2B bit[2] = '1'                                                                                     | 110  | 250 | 390  | mA   |

|                              | IBAT OCP Accuracy                   | IBAT_OCP_ACC              | Register 0x2D bit[2] = 1Rsense = $0.002\Omega$ , Register 0x02bit[6:0],range: 2A-10A, step: 100mAIBAT_OCP = 2A |      |     | 5    | %    |

| Parameter                 |                                 | Symbol                           | Test Conditions                                                                                                   | Min   | Тур  | Max   | Unit |

|---------------------------|---------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

|                           |                                 |                                  | IBAT_OCP = 6A                                                                                                     | -2    |      | 2     | %    |

|                           | TSBAT and TSBUS<br>OTP Accuracy | Ts_otp_acc                       | Falling edge, Register 0x28/0x29<br>bit[7:0]<br>range: 0–49.8%, step: 0.19531%                                    | -1    |      | 1     | %    |

|                           | TDIE_OTP Accuracy               | TDIE_OTP_ACC                     | Rising threshold                                                                                                  |       | 145  |       | °C   |

|                           | TDIE_OTP Hysteresis             | TDIE_OTP_HYS                     | OTP recovery, falling hysteresis                                                                                  |       | 30   |       | °C   |

|                           | VBUS_HIGH_ERR<br>Accuracy       | VBUS_HIGH_ERR_<br>ACC            | Detect VBUS/VOUT ratio, rising edge                                                                               | 2.328 | 2.4  | 2.472 | V/V  |

|                           | VBUS_LOW_ERR<br>Accuracy        | V <sub>BUS_LOW_ERR_</sub><br>ACC | Detect VBUS/VOUT ratio, falling<br>edge                                                                           | 2     | 2.04 | 2.08  | V/V  |

|                           | Converter OCP<br>Threshold      | I CON_OCP                        |                                                                                                                   |       | 16   |       | А    |

| Alarm<br>Threshold<br>and | VBUS_OVP_ALM<br>Accuracy        | VBUS_OVP_ALM_ACC                 | Register 0x07 bit[6:0],<br>range:6V–12.35V, step: 50mV<br>VBUS_OVP_ALM = 6V to 9V                                 | -0.5  |      | 0.5   | %    |

| Accuracy                  | VBUS_OVP_ALM<br>Hysteresis      | VBUS_OVP_ALM_HYS                 | Falling edge                                                                                                      |       | 50   |       | mV   |

|                           | VBAT_OVP_ALM<br>Accuracy        | VBAT_OVP_ALM_ACC                 | Register 0x01 bit[5:0],<br>range:3.5V–5.075V, step: 25mV<br>VBAT_OVP = 3.5V to 4.4V                               | -0.5  |      | 0.5   | %    |

|                           | VBAT_OVP_ALM<br>Hysteresis      | VBAT_OVP_ALM_HYS                 | Falling edge                                                                                                      |       | 50   |       | mV   |

|                           | IBUS_OCP_ALM<br>Accuracy        | IBUS_OCP_ACC                     | Register 0x08 bit[3:0],<br>range:1A–4.75A, step: 250mA<br>IBUS_OCP = 2A                                           | -10   |      | 10    | %    |

|                           | ,                               |                                  | IBUS_OCP = 4A                                                                                                     | -5    |      | 5     | %    |

|                           | IBUS_OCP_ALM<br>Hysteresis      | IBUS_OCP_ALM_HYS                 | Falling edge                                                                                                      |       | 50   |       | mA   |

|                           | IBAT_OCP_ALM<br>Accuracy        | IBAT_OCP_ALM_ACC                 | R <sub>SENSE</sub> = 0.002Ω, Register 0x02<br>bit[6:0],<br>range: 2A–10A, step: 100mA<br>IBAT_OCP = 2A            | -5    |      | 5     | %    |

|                           |                                 |                                  | IBAT_OCP = 6A                                                                                                     | -2    |      | 2     | %    |

|                           | IBAT_OCP_ALM<br>Hysteresis      | IBAT_OCP_ALM_HYS                 | Falling edge                                                                                                      |       | 100  |       | mA   |

|                           | IBAT_UCP_ALM<br>Accuracy        | IBAT_UCP_ALM_ACC                 | R <sub>SENSE</sub> = 0.002Ω, Register 0x04<br>bit[6:0],<br>range: 0–6.35A, step: 50mA<br>IBAT_UCP_ALM = 2A        | -5    |      | 5     | %    |

|                           | IBAT_UCP_ALM<br>Hysteresis      | IBAT_UCP_ALM_HYS                 | Falling edge                                                                                                      |       | 100  |       | mA   |

|                           | TSBAT_TSBUS_ALM<br>Accuracy     | Ts_otp_alm_acc                   | Falling edge, range:0–<br>50%,Step:0.19531%<br>TSBAT_TSBUS_ALM Threshold =<br>TSBAT_OTP + 4% or<br>TSBUS_OTP + 4% | -1    |      | 1     | %    |

|                           | TSBAT_TSBUS_ALM<br>Hysteresis   | Ts_otp_alm_alm_h<br>ys           | Rising edge                                                                                                       |       | 5    |       | %    |

|                           | TDIE_OTP_ALM<br>Accuracy        | TDIE_OTP_ALM_ACC                 | Register 0x2A bit[7:0],<br>range: 25°C –152.5°C, step: 0.5°C                                                      | -4    |      | 4     | °C   |

|                           | TDIE_OTP_ALM<br>Hysteresis      | TDIE_OTP_ALM_HYS                 | Falling edge                                                                                                      |       | 10   |       | °C   |

| Parameter                     |                                                                                                   | Symbol                           | Test Conditions                                               | Min   | Тур | Max        | Unit     |

|-------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------------------------------------|-------|-----|------------|----------|

| ADC                           | ADC Sample Rate                                                                                   | fsample_rate                     |                                                               |       | 10  |            | kHz      |

|                               | ADC Data Rate tDATA                                                                               | tdata_adc                        | 11bit, 8 averages report data for each channel                |       | 800 |            | μs       |

|                               | VBUS ADC Accuracy                                                                                 | VBUS_ADC_ACC                     | Range:0V-14V, VBUS = 8V                                       | -0.75 |     | 0.75       | %        |

|                               | IBUS ADC Accuracy                                                                                 | IBUS_ADC_ACC                     | Range:0–5A, IBUS = 4A                                         | -5    |     | 5          | %        |

|                               | VAC ADC Accuracy                                                                                  | VAC_ADC_ACC                      | Range:0V–14V, VAC = 8V                                        | -0.75 |     | 0.75       | %        |

|                               | VOUT ADC Accuracy                                                                                 | Vout_adc_acc                     | Range:0V–5V, VOUT = 4V                                        | -0.75 |     | 0.75       | %        |

|                               | VBAT ADC Accuracy                                                                                 | VBAT_ADC_ACC                     | Range:0V–5V, VBAT = 3.5V to<br>4.5V                           | -0.5  |     | 0.5        | %        |

|                               | IBAT ADC Accuracy                                                                                 | IBAT_ADC_ACC                     | Range:0–10A, IBAT = 6A,<br>R <sub>SENSE</sub> = $0.002\Omega$ | -2.5  |     | 2.5        | %        |

|                               | TDIE ADC Accuracy                                                                                 | TDIE_ADC_ACC                     | Range:0–150 °C, step: 0.5 °C                                  | -4    |     | 4          | °C       |

|                               | TSBUS ADC<br>Accuracy                                                                             | T <sub>SBUS_ADC_ACC</sub>        | Range:0–50%<br>TSBUS pin voltage = 0.2V to 2V                 | -1    |     | 1          | %        |

|                               | TSBAT ADC<br>Accuracy                                                                             | TSBAT_ADC_ACC                    | Range:0–50%<br>TSBAT pin voltage = 0.2V to 2V                 | -1    |     | 1          | %        |

|                               | Logic Input High<br>Voltage                                                                       |                                  | SCL, SDA vs GND                                               | 1.4   |     |            | V        |

|                               | Logic Input Low<br>Voltage                                                                        |                                  | SCL, SDA vs GND                                               |       |     | 0.5        | V        |

|                               | Logic Output Low<br>Voltage                                                                       | V <sub>OL</sub>                  | SDA vs GND                                                    |       |     | 0.4        | V        |

|                               | I <sup>2</sup> C Input Capacitance                                                                |                                  | SCL, SDA                                                      |       | 5   |            | pF       |

|                               | SCL Operating<br>Frequency                                                                        | f(SCL)                           |                                                               |       |     | 400        | kHz      |

|                               | Bus Free Time<br>Between Stop and<br>Start Conditions                                             | t(BUF)                           |                                                               | 1.3   |     |            | μs       |

| I <sup>2</sup> C<br>Interface | Hold Time after<br>Repeated Start<br>Condition. First Clock<br>is Generated after<br>this Period. | t <sub>(HDSTA)</sub>             |                                                               | 0.6   |     |            | μs       |

|                               | Repeated Start<br>Condition Setup Time                                                            | t(SUSTA)                         |                                                               | 0.6   |     |            | μs       |

|                               | Stop Condition Setup<br>Time                                                                      | t(susto)                         |                                                               | 0.6   |     |            | μs       |

|                               | Data Hold Time                                                                                    | t(hddat)                         |                                                               |       |     | 0.9        | μs       |

|                               | Data Setup Time                                                                                   | t(SUDAT)                         |                                                               | 100   |     |            | ns       |

|                               | SCL Clock Low<br>Period                                                                           | t(LOW)                           |                                                               | 1.3   |     |            | μs       |

|                               | SCL Clock High<br>Period                                                                          | t(HIGH)                          |                                                               | 0.6   |     |            | μs       |

|                               | Clock/Data Fall Time<br>Clock/Data Rise Time                                                      | t <sub>F</sub><br>t <sub>R</sub> |                                                               |       |     | 300<br>300 | ns<br>ns |

**Note 1:** Stresses beyond the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

9

**Note 2:** Package thermal resistance is measured in the natural convection at TA = 25°C on an 8.5cm×7.7cm size four-layer Silergy Evaluation Board.

Note 3: The device is not guaranteed to function outside its operating conditions.

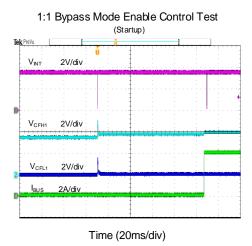

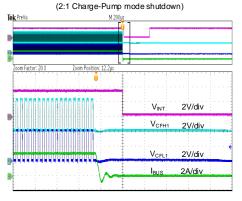

# **Typical Performance Characteristics**

$(V_{\text{IN}} = 13.5\text{V}, \text{L} = 4.7 \mu \text{H}(\text{CLF10040T-4R7M}), \text{R}_{\text{FSW}} = 62 \text{k}\Omega, \text{R}_{\text{CTRL}} = 10 \text{k}\Omega, \text{T}_{\text{A}} = 25^{\circ}\text{C}, \text{otherwise specified.})$

V<sub>CFL1</sub> 2V/div

Time (40µs/div)

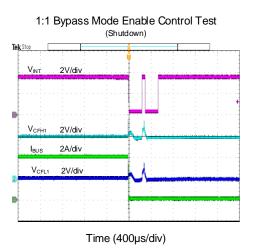

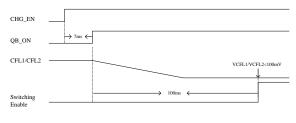

CHG\_EN Enable Control Test

Time (10µs/div)

DS\_SY20797C Rev. 1.0 © 2023 Silergy Corp.

Time (1µs/div)

### **Detailed Description**

#### Overview

The SY20797C is a high efficiency switched capacitor converter for high power fast charging applications. As a voltage divider or a current doubler with 50% switching duty cycle, it integrates extremely low  $R_{DS(ON)}$  MOSFETs to achieve 97% efficiency and up to 8A maximum charging current. It also provides a 9-channel, 12-bit ADC to monitor input and output voltage, current, and temperature for battery charging management by a host.

The SY20797C offers protection against multiple conditions, including external OVP-FET shutdown for input overvoltage protection, input overcurrent protection, output overvoltage and overcurrent protection, and temperature sensing for VBUS, battery, and die.

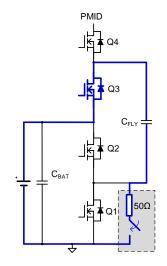

Figure 4. Single-Phase Switched Capacitor Converter

#### **OVP-FET Control**

The SY20797C's VAC and OVPGATE pins are used to monitor the adaptor voltage and control the external OVP-FET. As shown in Figure 5, the OVP-FET is driven by the OVPGATE pin if VAC pin voltage is higher than the  $V_{AC\_INSERT}$  threshold. To protect the low voltage device, OVP-FET will be turned off in less than 100ns if VAC pin voltage is higher than the  $V_{AC\_OVP}$  threshold. VAC overvoltage protection logic includes automatic recovery.

DS\_SY20797C Rev. 1.0 © 2023 Silergy Corp.

Figure 5. OVP-FET Control

#### Soft-Start

The SY20797C uses a pre-charge stage to charge the flying capacitor before switching. When the CHG\_EN bit is enabled, a 50 $\Omega$  resistor is connected to CFL1/CFL2 to limit the pre-charge current. At the end of the pre-charge time, the CFL1/CFL2 voltage is detected. If CFL1/CFL2 is pulled lower than 100mV, the pre-charge stage is considered complete. Otherwise, the pre-charge stage is considered as failing and SY20797C will report a 'CFLY\_DIG' fault, which means a CFLY short during converter soft-start.

Figure 6. Pre-Charge Circuit

Figure 7. Soft-Start

#### I<sup>2</sup>C Address and Mode Selection

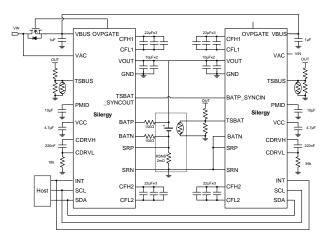

The CDRVL\_ADDRMS pin is used to set the default I<sup>2</sup>C address and mode as shown in Table 1. Two devices can be paralleled for higher charging power if they are configured as host and peripheral, respectively. For synchronization, the host's TSBAT\_SYNCOUT pin outputs a PWM signal to the peripheral's BATP\_SYNCIN pin to achieve phase interleaving.

#### Table 1: I<sup>2</sup>C Address and Mode Selection

| CDRVL_ADDRMS<br>Pin Resistor To<br>GND | l <sup>2</sup> C<br>Address | Mode       | V <sub>AC_OVP</sub><br>Default<br>Value |

|----------------------------------------|-----------------------------|------------|-----------------------------------------|

| 18kΩ                                   | 0x65                        | Host       | 6.5V                                    |

| 39kΩ                                   | 0x66                        | Peripheral | Disabled                                |

| 75kΩ                                   | 0x65                        | Standalone | 11V                                     |

| >150kΩ                                 | 0x66                        | Standalone | 6.5V                                    |

Figure 8. I<sup>2</sup>C Address and Mode Selection

# **Protection Modes**

#### **Overtemperature Protection**

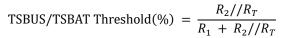

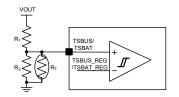

The SY20797C provides overtemperature protection for the junction, bus connector, and battery pack. If junction temperature is higher than 145°C, the SY20797C will stop charging and reset the CHG\_EN bit to '0'. For bus connector and battery pack temperature sensing, a resistor divider circuit is added as shown in Figure 9. RT is a negative coefficient thermistor and the protection threshold is calculated as follows:

Figure 9. Temperature Sensing

Note that TSBUS and TSBAT thresholds are percentages of VOUT that are programmable using registers 0x28 and 0x29, and VOUT ADC should be enabled if either TSBUS or TSBAT is used. As with junction temperature protection, the SY20797C will stop charging and reset the CHG\_EN bit to '0' if the TSBAT or TSBUS threshold is triggered.

#### **Overvoltage Protection**

The SY20797C provides overvoltage protection for VBUS, VOUT, and battery (battery voltage is sensed by BATP and BATN pins). If any of these voltage thresholds are triggered, the SY20797C will stop charging and reset the CHG\_EN bit to '0'. In high charging current applications, it is recommended that BATP and BATN pins connect a 100 $\Omega$  resistor to the battery pack positive and negative terminals.

Overvoltage protection and alarm thresholds VBUS\_OVP and VBUS\_OVP\_ALM are set by registers 0x06 and 0x07, respectively. In 2:1 charge-pump mode, the thresholds are directly set by these registers, while in 1:1 bypass mode the thresholds are divided by two.

#### **Overcurrent Protection**

The SY20797C provides overcurrent protection for BUS and battery. Input current IBUS is sensed by blocking FET Q<sub>B</sub>, and battery charging current detected by SRP and SRN pins is sensed by a  $5m\Omega/2m\Omega/1m\Omega$  resistor. If the IBUS OCP or IBAT OCP threshold is triggered, the SY20797C will stop charging and reset the CHG\_EN bit to '0'.

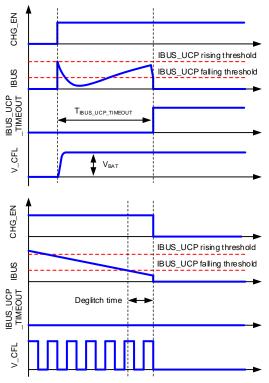

#### **Input Undercurrent Protection**

The SY20797C provides undercurrent protection ( $I_{BUS\_UCP}$ ) to prevent reverse current from battery to VBUS. When CHG\_EN is enabled, a counting timer with duration set by IBUS\_UCP\_TIMEOUT (register 0x2B) is activated. A timeout occurs and IBUS\_UCP\_TIMEOUT\_FLAG (register 0x0A) is set if the bus current is still below the IBUS\_UCP rising threshold when the timer expires. The IBUS\_UCP falling threshold will be enabled and the

counting timer will be disabled once IBUS is higher than the IBUS\_UCP rising threshold. If IBUS falls below the IBUS\_UCP falling threshold, IBUS\_UCP\_FALL will be triggered and the SY20797C will stop charging and reset the CHG\_EN bit to '0'. It should be noted that the IBUS\_UCP rising and falling thresholds are simultaneously set by IBUS\_UCP\_RISE\_THRESH (bit[2] of register 0x2B).

Figure 10. Input Undercurrent Protection

#### **VBUS** Range Protection

Before the device begins charging, VBUS should be approximately 2 × VOUT in 2:1 charge-pump mode and approximately VOUT in 1:1 bypass mode. The SY20797C has two fixed thresholds to monitor the ratio of VBUS and VOUT: V<sub>BUS\_HIGH\_ERR</sub> and V<sub>BUS\_LOW\_ERR</sub>. The SY20797C will begin soft-start and switching only when V<sub>BUS\_LOW\_ERR</sub> < V<sub>BUS</sub>/V<sub>OUT</sub> < V<sub>BUS\_HIGH\_ERR</sub> in 2:1 charge-pump mode and when V<sub>BUS\_LOW\_ERR</sub>/2 < V<sub>BUS</sub>/V<sub>OUT</sub> < V<sub>BUS\_HIGH\_ERR</sub>/2 in 1:1 bypass mode. After charging is enabled, the VBUS range protection will be disabled.

#### VBAT and IBAT Regulation

The SY20797C features an integrated regulation circuit to protect the battery and limit instantenous VBAT and IBAT

transients. For VBAT regulation, the monitored differential voltage between BATP and BATN pin, i.e., V<sub>BATP-BATN</sub>, is compared to VBAT\_REG threshold, and the drive voltage of OVP FET will be controlled to limit VBUS if V<sub>BATP-BATN</sub> is greater than VBAT\_REG threshold. As a result VBAT transients will be effectively reduced. For IBAT regulation, the monitored differential voltage between SRN and SRP pin is first converted into a current value I<sub>SRN-SRP</sub>, and then compared to the IBAT\_REG threshold. If I<sub>SRN-SRP</sub> exceeds IBAT\_REG, the drive voltage of OVP FET will be controlled to reduce VBUS, which in turn reduces the output voltage to limit instant IBAT transients. If regulation is triggered and persists for t<sub>REG\_TIMEOUT</sub>, the SY20797C will stop charging and reset the CHG\_EN bit to '0'.

#### Dropout Voltage Protection (VDR\_OVP)

In regulation status, the external OVP-FET operates in linear mode and might generate considerable power loss. The VDR\_OVP function monitors the voltage drop between the VAC and VBUS pins to prevent the OVP-FET and system from overheating. If the VDR\_OVP threshold is triggered, the SY20797C will stop charging and reset

the CHG\_EN bit to '0'.

#### Watchdog Timer

The SY20797C provides a watchdog timer to terminate charging if the device does not receive read or write commands before the watchdog timer expires. The CHG\_EN bit and ADC\_EN bit will be reset to '0' if this occurs.

#### INT

INT is an open-drain, active-low interrupt output pin. It should be pulled up by an external voltage source. When the SY20797C triggers an event, the INT pin will be pulled low for 256µs to notify the host, The corresponding STAT bit and FLAG bit will also be set to '1'. The STAT bit will be reset to '0' if the event is cleared. Read action or power reset can clear the FLAG bit. The MASK bit prevents the INT signal from being sent to the host, but will not stop the STAT and FLAG from updating.

# **Applications Schematic**

# **BOM List**

| Designator             | Description     | Part Number        | Manufacturer |

|------------------------|-----------------|--------------------|--------------|

| U1                     | PowerPAK SO-8   | SiR472DP           |              |

| CO                     | 4.7µF/25V, 0603 | GRM188R61E475KE11D | muRata       |

| C3, C4, C5, C6, C7, C8 | 22µF/10V, 0603  | GRM188R61A226ME15D | muRata       |

| C11, C12               | 1µF/25V, 0805   | GRM219R71E105KA88D | muRata       |

| C2, C9, C10            | 10µF/25V, 0805  | GRM21BR61E106KA73L | muRata       |

| C1                     | 220nF/50V, 0603 |                    |              |

| R6, R7                 | 100Ω, 0603      |                    |              |

| R13                    | 10Ω, 0603       |                    |              |

| RSNS                   | 2mΩ, 1206       |                    |              |

| R1                     | 75kΩ, 0603      |                    |              |

| R10, R11, R12          | 10kΩ, 0603      |                    |              |

| R2, R3, R8, R9         | 100kΩ, 0603     |                    |              |

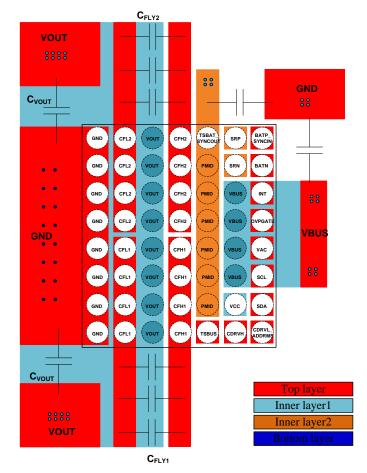

# Layout Design

Follow these PCB layout considerations for optimal performance and to prevent noise and electromagnetic interference:

- To minimize noise, place a typical X5R or better grade ceramic capacitor as close as possible to the VAC, BUS, PMID, and GND pins. Minimize the loop areas formed by C<sub>VAC</sub> and the VAC/GND pins, C<sub>BUS</sub> and the BUS/GND pins, and C<sub>PMID</sub> and the PMID/GND pins. A 10μF low ESR ceramic capacitor is recommended.

- To improve charge pump efficiency, use X5R or better grade low ESR ceramic capacitors for the flying

capacitors. Refer to the efficiency curve in the typical performance characteristics to select capacitor value. The flying capacitors should be placed as close as possible to the SY20797C on the same layer.

The output capacitor is selected to handle the output ripple noise requirements. Use a low ESR ceramic capacitor with voltage rating higher than the maximum output voltage. The output capacitance should be at least 10µF × 2 ceramic capacitors.

# **Register Map**

I<sup>2</sup>C Peripheral Address: 0x66 (standalone1), 0x65 (standalone2), 0x66 (peripheral), 0x65 (host).

| Register | ACRONYM                             |            | Default    | t Value    |      |

|----------|-------------------------------------|------------|------------|------------|------|

| Register |                                     | Standlone1 | Standlone2 | Peripheral | Host |

| 0x00     | VBAT_OVP and Charge<br>Mode Control | 0x22       | 0x22       | 0xA2       | 0x22 |

| 0x01     | VBAT_OVP_ALM                        | 0x1C       | 0x1C       | 0x9C       | 0x1C |

| 0x02     | IBAT_OCP                            | 0x3D       | 0x3D       | 0xBD       | 0x3D |

| 0x03     | IBAT_OCP_ALM                        | 0x3C       | 0x3C       | 0xBC       | 0x3C |

| 0x04     | IBAT_UCP                            | 0x28       | 0x28       | 0xA8       | 0x28 |

| 0x05     | AC_PROTECTION                       | 0x07       | 0x00       | 0x00       | 0x07 |

| 0x06     | VBUS_OVP                            | 0x3A       | 0x3A       | 0x3A       | 0x3A |

| 0x07     | VBUS_OVP_ALM                        | 0x38       | 0x38       | 0xB8       | 0x38 |

| 0x08     | IBUS_OCP_UCP                        | 0x0D       | 0x0D       | 0x0D       | 0x0D |

| 0x09     | IBUS_OCP_ALM                        | 0x50       | 0x50       | 0x50       | 0x50 |

| 0x0A     | CONVERTER_STATE                     | 0x00       | 0x00       | 0x00       | 0x00 |

| 0x0B     | CHG_CTL                             | 0x40       | 0x40       | 0x40       | 0x40 |

| 0x0C     | CHG_CTL1                            | 0x00       | 0x00       | 0x20       | 0x46 |

| 0x0D     | INT_STAT                            | 0x00       | 0x00       | 0x00       | 0x00 |

| 0x0E     | INT_FLAG                            | 0x00       | 0x00       | 0x00       | 0x00 |

| 0x0F     | INT_MASK                            | 0x00       | 0x00       | 0x00       | 0x00 |

| 0x10     | FLT_STAT                            | 0x00       | 0x00       | 0x00       | 0x00 |

| 0x11     | FLT_FLAG                            | 0x00       | 0x00       | 0x00       | 0x00 |

| 0x12     | FLT_MASK                            | 0x00       | 0x00       | 0x00       | 0x00 |

| 0x13     | DEVICE_INFO                         | 0x0E       | 0x0E       | 0x0E       | 0x0E |

| 0x14     | ADC_CTL                             | 0x00       | 0x00       | 0x00       | 0x00 |

| 0x15     | AD_ EN                              | 0x00       | 0x00       | 0xF8       | 0x06 |

| 0x16     | IBUS_ADC1                           | 0x00       | 0x00       | 0x00       | 0x00 |

| 0x17     | IBUS_ADC0                           | 0x00       | 0x00       | 0x00       | 0x00 |

| 0x18     | VBUS_ADC1                           | 0x00       | 0x00       | 0x00       | 0x00 |

| 0x19     | VBUS_ADC0                           | 0x00       | 0x00       | 0x00       | 0x00 |

| 0x1A     | VAC_ADC1                            | 0x00       | 0x00       | 0x00       | 0x00 |

| 0x1B | VAC_ADC0      | 0x00 | 0x00 | 0x00 | 0x00 |

|------|---------------|------|------|------|------|

| 0x1C | VOUT_ADC1     | 0x00 | 0x00 | 0x00 | 0x00 |

| 0x1D | VOUT_ADC0     | 0x00 | 0x00 | 0x00 | 0x00 |

| 0x1E | VBAT_ADC1     | 0x00 | 0x00 | 0x00 | 0x00 |

| 0x1F | VBAT_ADC0     | 0x00 | 0x00 | 0x00 | 0x00 |

| 0x20 | IBAT_ADC1     | 0x00 | 0x00 | 0x00 | 0x00 |

| 0x21 | IBAT_ADC0     | 0x00 | 0x00 | 0x00 | 0x00 |

| 0x22 | TSBUS_ADC1    | 0x00 | 0x00 | 0x00 | 0x00 |

| 0x23 | TSBUS_ADC0    | 0x00 | 0x00 | 0x00 | 0x00 |

| 0x24 | TSBAT_ADC1    | 0x00 | 0x00 | 0x00 | 0x00 |

| 0x25 | TSBAT_ADC0    | 0x00 | 0x00 | 0x00 | 0x00 |

| 0x26 | TDIE_ADC1     | 0x00 | 0x00 | 0x00 | 0x00 |

| 0x27 | TSBAT_ADC0    | 0x00 | 0x00 | 0x00 | 0x00 |

| 0x28 | TSBUS_OTP     | 0x15 | 0x15 | 0x15 | 0x15 |

| 0x29 | TSBAT_OTP     | 0x15 | 0x15 | 0x15 | 0x15 |

| 0x2A | TDIE_ALM      | 0xC8 | 0xC8 | 0xC8 | 0xC8 |

| 0x2B | REG_CTL       | 0xE0 | 0xE0 | 0xE0 | 0xE0 |

| 0x2C | REG_THRESHOLD | 0x00 | 0x00 | 0x00 | 0x00 |

| 0x2D | REG_FLAG      | 0x00 | 0x00 | 0x00 | 0x00 |

| 0x2E | REG_STAT_FLAG | 0x00 | 0x00 | 0x00 | 0x00 |

# Register reset map

| Reset by Watchdog of Register 0x0B bit[2:0] |                               |                 |                                    |  |  |  |

|---------------------------------------------|-------------------------------|-----------------|------------------------------------|--|--|--|

| Register                                    | Bit and Name                  | Register        | Bit and Name                       |  |  |  |

| 0x0C                                        | Bit[7]: CHG_EN                | 0x14            | Bit[7]: ADC_EN                     |  |  |  |

| i                                           | Not reset by REG_RS           | T of Register 0 | 0B bit[7]                          |  |  |  |

| Register                                    | Bit and Name                  | Register        | Bit and Name                       |  |  |  |

| 0x05                                        | Bit[4]: VDR_OVP_THRESHOLD_SET | 0x11            | All bits of FLT_FLAG register      |  |  |  |

|                                             | Bit[3]: IBUS_UCP_TIMEOUT_FLAG |                 | Bit[7:5]: IBUS_UCP_TIMEOUT         |  |  |  |

| 0x0A                                        | Bit[2]: SWITCHING_STAT        |                 | Bit[4]: REG_EN                     |  |  |  |

|                                             | Bit[1]: CON_OCP_FLAG          | 0x2B            | Bit[3]: VOUT_OVP_DIS               |  |  |  |

| 0x0B                                        | Bit[6:4]: FSW_SET             | -   -           | Bit[1]: IBAT_RSEN                  |  |  |  |

| 0x0D                                        | All bits of INT_STAT register | 0x2C            | All bits of REG_THRESHOLD register |  |  |  |

| 0x0E                                        | All bits of INT_FLAG register | 0x2D            | All bits of REG_FLAG register      |  |  |  |

| 0x10                                        | All bits of FLT_STAT register |                 |                                    |  |  |  |

### VBAT\_OVP and Charge Mode Control Register (Register 0x00)

| Bit   | R/W | Default |                     | Description                                                                                                                                |

|-------|-----|---------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | R/W | 0       | VBAT_OVP_DIS        | Battery OVP enable bit.<br>0: Enable (default)<br>1: Disable<br>Read only and default = 1 for peripheral                                   |

| [6]   | R/W | 0       | Charge mode control | Charge mode selecting bit, CH_EN must<br>be set to '1' to start charging.<br>0: Forward 2:1 charge-pump mode<br>1: Forward 1:1 bypass mode |

| [5:0] | R/W | 10_0010 | VBAT_OVP            | Battery OVP threshold<br>VBAT_OVP = 3.5V + bit[5:0] × LSB<br>(default: 4.35V)<br>LSB = 25mV                                                |

#### VBAT\_OVP\_ALM Register (Register 0x01)

| Bit   | R/W | Default | Description            |                                                                                                                |  |

|-------|-----|---------|------------------------|----------------------------------------------------------------------------------------------------------------|--|

| [7]   | R/W | 0       | VBAT_OVP_ALM_DIS       | Battery OVP alarm enable bit.<br>0: Enable (default)<br>1: Disable<br>Read only and default = 1 for peripheral |  |

| [6]   | R   | 0       | Reserved               |                                                                                                                |  |

| [5:0] | R/W | 01_1100 | VBAT_OVP_ALM threshold | Battery OVP alarm threshold.<br>VBAT_OVP_ALM = 3.5V + bit[5:0] × LSB<br>(default: 4.2V)<br>LSB = 25mV          |  |

#### IBAT\_OCP Register (Register 0x02)

| Bit   | R/W | Default  | Description  |                                                                                                                                   |

|-------|-----|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------|

| [7]   | R/W | 0        | IBAT_OCP_DIS | Battery OCP enable bit.<br>0: Enable (default)<br>1: Disable<br>Read only and default = 1 for peripheral                          |

| [6:0] | R/W | 011_1101 | IBAT_OCP     | Battery OCP threshold.<br>IBAT_OCP = 2A + bit[6:0] × LSB<br>(default: 8.1A)<br>LSB = 100mA<br>Any setting over 10A is set to 10A. |

| _ | IBAT_OCP_ALM Register (Register 0x03) |     |         |                 |                                                                                                                |  |

|---|---------------------------------------|-----|---------|-----------------|----------------------------------------------------------------------------------------------------------------|--|

|   | Bit                                   | R/W | Default | Description     |                                                                                                                |  |

|   | [7]                                   | R/W | 0       | IBAT_OCP_ALM_IS | Battery OCP alarm enable bit.<br>0: Enable (default)<br>1: Disable<br>Read only and default = 1 for peripheral |  |

| [6:0] | R/W | 011_1100 | IBAT_OCP _ALM | Battery OCP alarm threshold.<br>IBAT_OCP_ALM = 2A + bit[6:0] × LSB<br>(default: 8A)<br>LSB = 100mA |

|-------|-----|----------|---------------|----------------------------------------------------------------------------------------------------|

|-------|-----|----------|---------------|----------------------------------------------------------------------------------------------------|

| Bit   | R/W | Default  | Description      |                                                                                                                |  |  |

|-------|-----|----------|------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| [7]   | R/W | 0        | IBAT_UCP_ALM_DIS | Battery UCP alarm enable bit.<br>0: Enable (default)<br>1: Disable<br>Read only and default = 1 for peripheral |  |  |

| [6:0] | R/W | 010_1000 | IBAT_UCP_ALM     | Battery UCP alarm threshold.<br>IBAT_UCP_ALM = bit[6:0] × LSB<br>(default: 2A)<br>LSB = 50mA                   |  |  |

#### IBAT\_UCP\_ALM Register (Register 0x04)

| AC_PROTECTION Register (Register 0x05) |     |         |                       |                                                                                                                                                                                                            |  |

|----------------------------------------|-----|---------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit                                    | R/W | Default |                       | Description                                                                                                                                                                                                |  |

| [7]                                    | R   | 0       | VAC_OVP_STAT          | Set 1 when a VAC_OVP event occurs.<br>Persists until condition is no longer valid.<br>0: No VAC_OVP fault<br>1: VAC_OVP fault is occurring                                                                 |  |

| [6]                                    | R   | 0       | VAC_OVP_FLAG          | VAC_OVP event. Cleared upon read.<br>0: No VAC_OVP fault<br>1: VAC_OVP fault has occurred                                                                                                                  |  |

| [5]                                    | R/W | 0       | VAC_OVP_MASK          | Mask VAC_OVP event to send INT.<br>0: Not masked (default)<br>1: Masked                                                                                                                                    |  |

| [4]                                    | R/W | 0       | VDR_OVP_THRESHOLD_SET | Voltage difference between VAC and<br>VBUS that will cause the device to stop<br>switching.<br>0: 300mV (default)<br>1: 400mV                                                                              |  |

| [3]                                    | R/W | 0       | VDR_OVP_DEGLITCH_SET  | Deglitch time after the device reaches the<br>VDR_OVP threshold before the device<br>stops switching.<br>0: 8µs (default)<br>1: 5ms                                                                        |  |

| [2:0]                                  | R/W | 111     | VAC_OVP               | 000-110 setting is determined by<br>VAC_OVP = $11V + bit[3:0] \times 1V$ .<br>Writing 1 to all of these bits sets the<br>VAC_OVP to 6.5V.<br>Default for peripheral = 000<br>Default for standalone2 = 000 |  |

#### VBUS\_OVP Register (Register 0x06)

| Bit   | R/W | Default  | Description |                                                                                                                                                                                                   |  |

|-------|-----|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [7]   | R/W | 0        | VBUS_PD_EN  | VBUS pulldown resistor enable bit.<br>0: Pulldown disable (default)<br>1: Pulldown enable (1kΩ resistor)                                                                                          |  |

| [6:0] | R/W | 011_1010 | VBUS_OVP    | VBUS OVP threshold.<br>2:1 charge-pump mode:<br>VBUS_OVP = $6V + bit[6:0] \times 50mV$ ,<br>Default = $8.9V$<br>1:1 bypass mode:<br>VBUS_OVP = $3V + bit[6:0] \times 25mV$ ,<br>Default = $4.45V$ |  |

|       | VBUS_OVP_ALM Register (Register 0x07) |          |                  |                                                                                                                                                                                      |  |  |

|-------|---------------------------------------|----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit   | R/W                                   | Default  | Description      |                                                                                                                                                                                      |  |  |

| [7]   | R/W                                   | 0        | VBUS_OVP_ALM_DIS | VBUS OVP alarm disable bit.<br>0: Enable (default)<br>1: Disable<br>Read only and default = 1 for peripheral                                                                         |  |  |

| [6:0] | R/W                                   | 011_1000 | VBUS_OVP_ALM     | VBUS OVP alarm threshold.<br>2:1 charge-pump mode:<br>VBUS_OVP_ALM = 6V + bit[6:0] ×50mV<br>Default: 8.8V<br>1:1 bypass mode:<br>VBUS_OVP_ALM = 3V + bit[6:0] ×25mV<br>Default: 4.4V |  |  |

### IBUS\_OCP\_UCP Register (Register 0x08)

| Bit | R/W | Default |                    | Description                                                                                                                                                          |

|-----|-----|---------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7] | R/W | 0       | IBUS_OCP_DIS       | IBUS_OCP disable bit.<br>0: Enable (default)<br>1: Disable                                                                                                           |

| [6] | R   | 0       | IBUS_UCP_RISE_FLAG | Set 1 and send an INT when IBUS current<br>is higher than IBUS_UCP_RISE threshold.<br>Clear upon read.<br>0: No IBUS_UCP_RISE<br>1: IBUS_UCP_RISE event has occurred |

| [5] | R/W | 0       | IBUS_UCP_RISE_MASK | Masks an IBUS_UCP_RISE event to send<br>an INT<br>0: Not masked (default)<br>1: Masked                                                                               |

| [4] | R   | 0       | IBUS_UCP_FALL_FLAG | Set 1 and send an INT when IBUS current<br>lower than IBUS_UCP_FALL threshold.<br>Clear upon read.<br>0: No IBUS_UCP_FALL<br>1:IBUS_UCP_FALL event has occurred      |

| [3:0] | R/W                                   | 1101     | IBUS_OCP         | IBUS OCP threshold<br>IBUS_OCP = 1A + bit[3:0] × 250mA,<br>Default: 4.25A   |

|-------|---------------------------------------|----------|------------------|-----------------------------------------------------------------------------|

|       | IBUS_OCP_ALM Register (Register 0x09) |          |                  |                                                                             |

| Bit   | R/W                                   | Default  |                  | Description                                                                 |

| [7]   | R/W                                   | 0        | IBUS_OCP_ALM_DIS | IBUS_OCP_ALM disable bit<br>0: Enable (default)<br>1: Disable               |

| [6:0] | R/W                                   | 101_0000 | IBUS_OCP_ALM     | IBUS OCP alarm threshold.<br>IBUS_OCP_ALM = bit[6:0] × 50mA,<br>Default: 4A |

|     | CONVERTER_STATE Register (Register 0x0A) |         |                       |                                                                                                                                                                                                               |  |  |  |

|-----|------------------------------------------|---------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit | R/W                                      | Default |                       | Description                                                                                                                                                                                                   |  |  |  |

| [7] | R                                        | 0       | TDIE_OTP_FLAG         | Set 1 and send an INT when die<br>temperature is higher than TDIE<br>threshold. Clear upon read.<br>0: Normal<br>1: TDIE OTP has occurred                                                                     |  |  |  |

| [6] | R                                        | 0       | TDIE_OTP_STAT         | Set 1 when die temperature is higher than<br>TDIE threshold. Persists until condition is<br>no longer valid.<br>0: Normal<br>1: TDIE_OTP is occurring                                                         |  |  |  |

| [5] | R                                        | 0       | VBUS_LOW_ERR_FLAG     | Set 1 and send an INT when VBUS/VOUT<br>is lower than VBUS_LOW_ERR threshold.<br>Clear upon read.<br>0: Normal<br>1: VBUS_LOW_ERR has occurred                                                                |  |  |  |

| [4] | R                                        | 0       | VBUS_HIGH_ERR_FLAG    | Set 1 and send an INT when VBUS/VOUT<br>is higher than VBUS_HIGH_ERR<br>threshold. Clear upon read.<br>0: Normal<br>1: VBUS_HGIH_ERR has occurred                                                             |  |  |  |

| [3] | R                                        | 0       | IBUS_UCP_TIMEOUT_FLAG | Set 1 and send an INT when IBUS is not<br>ramped to the IBUS_UCP_RISE threshold<br>in IBUS_UCP_TIMEOUT time after<br>CHG_EN = 1. Cleared upon read.<br>0: Normal<br>1: IBUS_UCP_TIMEOUT has occurred          |  |  |  |

| [2] | R                                        | 0       | SWITCHING_STAT        | Set 1 and send an INT when the converter<br>starts switching and<br>IBUS_UCP_TIMEOUT timer start. Only<br>one INT is sent when switching starts.<br>Persists until condition is no longer valid.<br>0: Normal |  |  |  |

|     |   |   |                | 1: SWITCHING is occurring                                                                                                                     |

|-----|---|---|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| [1] | R | 0 | CON_OCP_FLAG   | Set 1 and send an INT when converter<br>current is higher than CON_OCP<br>threshold. Clear upon read.<br>0: Normal<br>1: CON_OCP has occurred |

| [0] | R | 0 | CFLY_DIAG_FLAG | Set 1 and send an INT when CFLY shorts<br>during converter soft-start. Clear upon<br>read.<br>0: Normal<br>1: CFLY_DIG has occurred           |

| CHG_CTL Register (Register 0x0B) |     |         |           |                                                                                                                                                             |  |

|----------------------------------|-----|---------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit                              | R/W | Default |           | Description                                                                                                                                                 |  |

| [7]                              | R/W | 0       | REG_RST   | Register reset.<br>0: No register reset (default)<br>1: Reset registers                                                                                     |  |

| [6:4]                            | R/W | 100     | FSW_SET   | Set the switching frequency.<br>000: 250kHz<br>001: 250kHz<br>010: 300kHz<br>011: 375kHz<br>100: 500kHz(default)<br>101: 750kHz<br>110: 850kHz<br>111: 1MHz |  |

| [3]                              | R   | 0       | WDT_FLAG  | Set 1 and send an INT upon watchdog<br>timeout. Clear upon read.<br>0: Normal<br>1: WDT has occurred                                                        |  |

| [2]                              | R/W | 0       | WDT_DIS   | Watchdog disable.<br>0: Enabled (default)<br>1: Disabled                                                                                                    |  |

| [1:0]                            | R/W | 00      | WDT_TIMER | Watchdog timer setting.<br>00: 0.5s (default)<br>01: 1s<br>10: 5s<br>11: 30s                                                                                |  |

| CHG | CTL1 | Register | (Register 0x0C) |  |

|-----|------|----------|-----------------|--|

|     |      |          | (               |  |

| Bit | R/W | Default | Description |                                                                          |

|-----|-----|---------|-------------|--------------------------------------------------------------------------|

| [7] | R/W | 0       | CHG_EN      | Charger control bit.<br>0: Charger disable (default)<br>1: Charge enable |

| [6:5] | R   | 00 | MS            | Host, peripheral, or standalone operation.<br>00: Standalone<br>01: Peripheral<br>1x: Host                                                                                                                      |

|-------|-----|----|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4:3] | R/W | 00 | CHG_FSHIFT    | Adjust switching frequency for EMI.<br>00: Nominal frequency (default)<br>01: Nominal frequency + 10%<br>10: Nominal frequency - 10%<br>11: Spread spectrum enable for EMI, +/-<br>10% nominal frequency change |

| [2]   | R/W | 0  | TSBUS_OTP_DIS | TSBUS over-temperature protection<br>disable bit.<br>0: Enable (default)<br>1: Disable<br>Default for host = 1                                                                                                  |

| [1]   | R/W | 0  | TSBAT_OTP_DIS | TSBAT over-temperature protection<br>disable bit.<br>0: Enable (default)<br>1: Disable<br>Default for host = 1                                                                                                  |

| [0]   | R/W | 0  | TDIE_OTP_DIS  | TDIE over-temperature protection disable<br>bit.<br>0: Enable (default)<br>1: Disable                                                                                                                           |

### INT\_STAT Register (Register 0x0D)

| Bit | R/W | Default |                   | Description                                                                                                                                            |

|-----|-----|---------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7] | R   | 0       | VBAT_OVP_ALM_STAT | Set 1 when VBAT is higher than<br>VBAT_OVP_ALM threshold. Persists until<br>condition is no longer valid.<br>0: Normal<br>1: VBAT_OVP_ALM is occurring |

| [6] | R   | 0       | IBAT_OCP_ALM_STAT | Set 1 when IBAT is higher than<br>IBAT_OCP_ALM threshold. Persists until<br>condition is no longer valid.<br>0: Normal<br>1: IBAT_OCP_ALM is occurring |

| [5] | R   | 0       | VBUS_OVP_ALM_STAT | Set 1 when VBUS is higher than<br>VBUS_OVP_ALM threshold. Persists until<br>condition is no longer valid.<br>0: Normal<br>1: VBUS_OVP_ALM is occurring |

| [4] | R   | 0       | IBUS_OCP_ALM_STAT | Set 1 when IBUS is higher than<br>IBUS_OCP_ALM threshold. Persists until<br>condition is no longer valid.<br>0: Normal<br>1: IBUS_OCP_ALM is occurring |