### 2 to 1 Power MUX for USB PD Application

### **General Description**

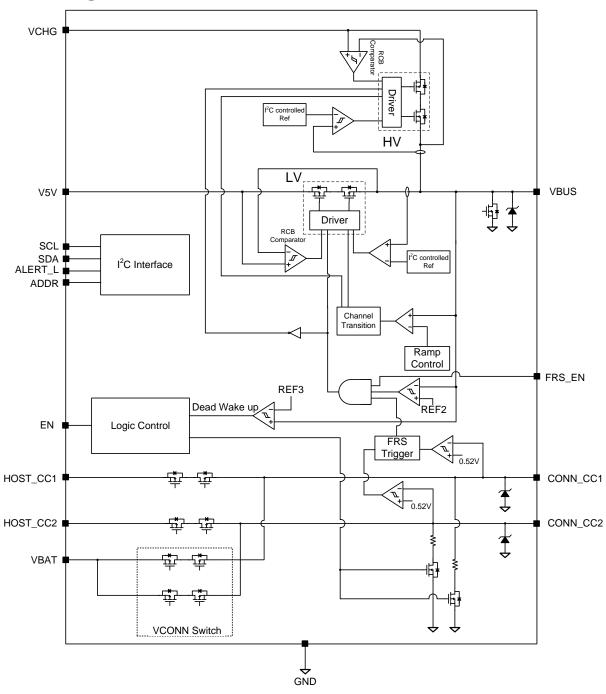

The SY6862B is a 2 to 1 power MUX switch for USB PD application. The SY6862B integrates two low on resistance power paths: high voltage power path and 5V voltage power path. The high voltage power path is a bi-directional channel. It can be configured as sink port or source port. Both directions have reverse block function.

The SY6862B is integrated CC bypass path. HOST\_CCx is isolated to CONN\_CCx when dead battery or VCONN is applied. If CONN\_CCx is selected as CC line, CONN\_CCx can be bypassed to HOST\_CCx by I<sup>2</sup>C control.

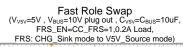

SY6862B support USB PD fast role swap. Once detected VBUS is lower than 4.75V, the high voltage channel will be shut down and the 5V power path will be turned on in 100us and act as a new source.

## **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY6862BQLC      | QFN3×4-16    |      |

#### **Features**

- 2 to 1 Power MUX:

- ➤ High Voltage Channel: 4.5V to 23V for VCHG Input Range.

- > 5V Channel: 4V to 5.5V for V5V Input Range

- Smooth Ramp Control When Channel Transition

- Reverse Blocking Function

- Bi-direction Control for High Voltage Channel

- Fast Role Swap

- I<sup>2</sup>C Interface

- CC Bypass and Isolation Control

- Dead Battery Wake up Function

- VCONN Path for E-mark Cable

- Protection:

- Output Current Limit Setting

- ➤ OCP/OVP/TSD/UVP

- RoHS Compliant and Halogen Free

- Compact Package QFN3×4-16

### **Applications**

- USB PD

- Desktop PC

- Laptop PC

- Smart Phone

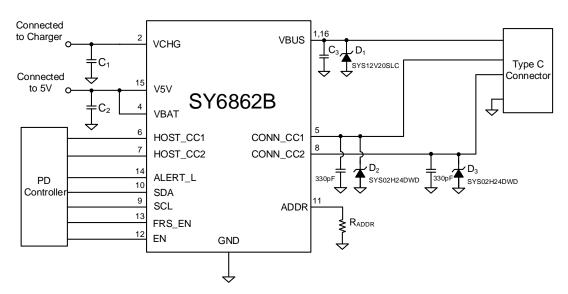

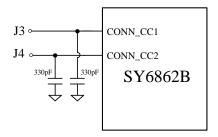

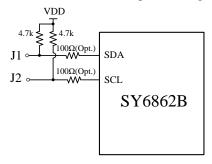

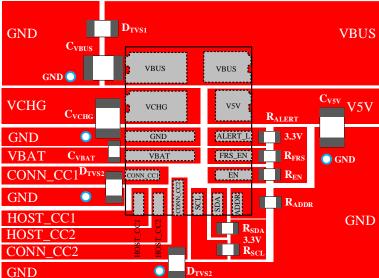

## **Typical application**

Fig.1 Schematic diagram

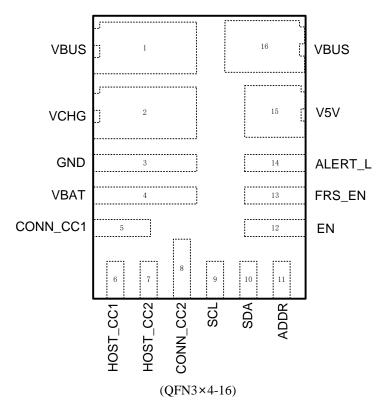

## Pin-out (top view)

Top mark: ECExyz (Device code: ECE, x=year code, y=week code, z= lot number code)

| Pin Name | Pin Number | Pin Description                                                                                                      |

|----------|------------|----------------------------------------------------------------------------------------------------------------------|

| VBUS     | 1,16       | Connector VBUS pin. Input/output and discharge switches, and powers the IC in the dead battery case.                 |

| VCHG     | 2          | 4.5V to 23V power input pin. Decouple this pin to PGND with a ceramic capacitor.                                     |

| GND      | 3          | Ground pin.                                                                                                          |

| VBAT     | 4          | 2.5V to 5.5V battery input to provide VCONN power.                                                                   |

| CONN_CC1 | 5          | Connect to Type C connector CC1.                                                                                     |

| HOST_CC1 | 6          | Connect to the host's Type C port controller's CC1 pin.                                                              |

| HOST_CC2 | 7          | Connect to the host's Type C port controller's CC2 pin.                                                              |

| CONN_CC2 | 8          | Connect to Type C connector CC2.                                                                                     |

| SCL      | 9          | I <sup>2</sup> C Interface serial clock pin. Logic level input.                                                      |

| SDA      | 10         | I <sup>2</sup> C Interface serial data pin. Logic level input/output.                                                |

| ADDR     | 11         | The device address set pin. Connect a resistor to GND to program the I <sup>2</sup> C address.                       |

| EN       | 12         | Enable control. Pull high to active the device.                                                                      |

| FRS_EN   | 13         | Fast role swap function enable pin. Pull high to enable FRS function. Pull low to disable. Do not leave it floating. |

| ALERT_L  | 14         | Open drain output to signal interrupts. Externally pulled up.                                                        |

| V5V      | 15         | 5V input; Provides power for 5V out. Also powers the IC in normal operation.                                         |

## **Block Diagram**

Figure 2. Block Diagram

| Absolute Maximum Ratings (Note 1)                                            |        |

|------------------------------------------------------------------------------|--------|

| VCHG                                                                         |        |

| V5V, VBAT                                                                    |        |

| CONN CCx                                                                     |        |

| VBUS                                                                         |        |

| EN, FRS                                                                      |        |

| SCL, SDA, ADDR, ALERT L, HOST CCx                                            |        |

| Power Dissipation, P <sub>D</sub> @ T <sub>A</sub> = 25°C QFN3×4             | 2.2W   |

| Package Thermal Resistance (Note 2)                                          |        |

| $	heta_{	ext{	iny JA}}$                                                      | 45°C/W |

| $\theta_{_{ m JC}}^{_{ m JC}}$                                               |        |

| Junction Temperature Range                                                   |        |

| Lead Temperature (Soldering, 10 sec.)                                        |        |

| Storage Temperature Range                                                    |        |

| ESD Susceptibility (Note 2)  HBM (Human Body Mode)  VBUS, CONN_CC1, CONN_CC2 |        |

| CDM (Charged Device Mode)                                                    |        |

| All Pins                                                                     | 500V   |

| Recommended Operating Conditions (Note 3)                                    |        |

| VCHG                                                                         |        |

| V5V, VBAT                                                                    |        |

| CONN_CCx                                                                     |        |

| VBUS, EN, FRS                                                                |        |

| SCL, SDA, ADDR, ALERT_L, HOST_CCx                                            |        |

| Junction Temperature Range                                                   |        |

| Ambient Temperature Range                                                    |        |

### **Electrical Characteristics**

$(V5V = 5V, VCHG = 20V, T_A = 25$ °C,  $I_{OUT} = 1A$ . Unless otherwise specified)

| Parameter                                             | Symbol                    | Test Conditions                                                                                                                            | Min | Тур | Max  | Unit |

|-------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Voltage Range for Charger<br>Pin                      | $V_{CHG}$                 |                                                                                                                                            | 4.5 |     | 23   | V    |

| Voltage Range for VBUS                                | $V_{\mathrm{BUS}}$        |                                                                                                                                            | 4.0 |     | 25   | V    |

| Voltage Range for V5V                                 | $V_{V5V}$                 |                                                                                                                                            | 4.0 |     | 5.5  | V    |

| Voltage Range for VBAT                                | $V_{BAT}$                 |                                                                                                                                            | 2.5 |     | 5.5  | V    |

| Under Voltage Protection for VCHG                     | V <sub>UVP_CHG</sub>      |                                                                                                                                            |     |     | 4.4  | V    |

| Hysteresis of Under<br>Voltage Protection for<br>VCHG | V <sub>UVP_CHG_HYS</sub>  |                                                                                                                                            |     | 0.2 |      | V    |

| Under Voltage Protection for VBUS                     | V <sub>UVP_VBUS</sub>     |                                                                                                                                            |     |     | 3.9  | V    |

| Hysteresis of Under<br>Voltage Protection for<br>VBUS | V <sub>UVP_VBUS_HYS</sub> |                                                                                                                                            |     | 0.1 |      | V    |

| Under Voltage protection for V5V                      | $V_{UVP\_V5V}$            |                                                                                                                                            |     |     | 3.9  | V    |

| Hysteresis Under Voltage protection for V5V           | V <sub>UVP_V5V_HYS</sub>  |                                                                                                                                            |     | 0.2 |      | V    |

| Under Voltage Protection for VBAT                     | V <sub>UVP_BAT</sub>      |                                                                                                                                            |     |     | 2.45 | V    |

| Hysteresis Under Voltage<br>Protection for V5V        | V <sub>UVP_BAT_HYS</sub>  |                                                                                                                                            |     | 0.1 |      | V    |

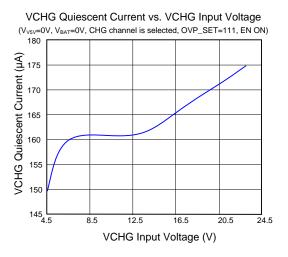

|                                                       | I <sub>Q_CHG</sub>        | V <sub>CHG</sub> =20V, V <sub>V5V</sub> =0V, EN=1,<br>V <sub>BAT</sub> =0V, OVP_SET=111, Null load.<br>HV channel is selected, source mode |     | 200 |      | μΑ   |

|                                                       | TQ_CHG                    | V <sub>CHG</sub> =20V, V <sub>V5V</sub> =5V, EN=1,<br>V <sub>BAT</sub> =0V, OVP_SET=111, Null load.<br>V5V channel is selected             |     | 200 |      | μΑ   |

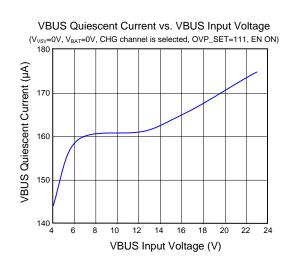

| Quiescent Current                                     | $I_{Q\_VBUS}$             | VBUS =20V, V <sub>V5V</sub> =0V, EN=1,<br>OVP_SET=111, VOUT null load.<br>HV channel is selected, sink mode                                |     | 200 |      | μΑ   |

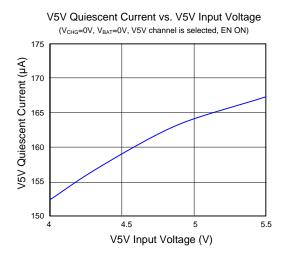

|                                                       | $I_{Q\_V5V}$              | V <sub>CHG</sub> =0V, V <sub>V5V</sub> =5V, EN=1,<br>V <sub>BAT</sub> =0V, OVP_SET=111, Null load.<br>V5V channel is selected              |     | 200 |      | μΑ   |

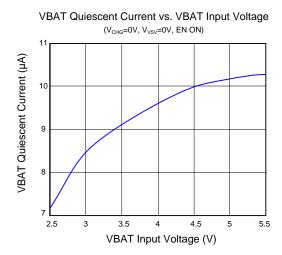

|                                                       | $I_{Q\_BAT}$              | V <sub>CHG</sub> =0V, V <sub>V5V</sub> =0V, EN=1,<br>V <sub>BAT</sub> =5V, OVP_SET=111, Null load.                                         |     | 10  |      | μΑ   |

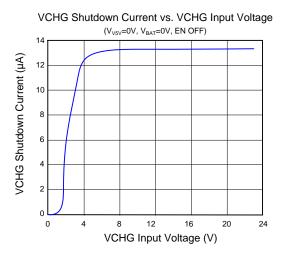

|                                                       | ī                         | V <sub>CHG</sub> =20V, V <sub>V5V</sub> =0V, EN=0,<br>V <sub>BAT</sub> =0V, OVP_SET=111, Null load.                                        |     | 15  |      | μΑ   |

| Shutdown Current                                      | I <sub>SHDN_CHG</sub>     | V <sub>CHG</sub> =20V, V <sub>V5V</sub> =5V, EN=0,<br>V <sub>BAT</sub> =0V, OVP_SET=111, Null load.                                        |     | 20  |      | μΑ   |

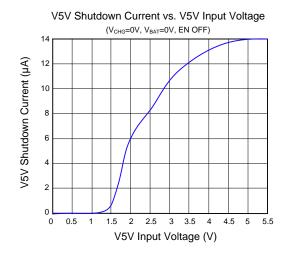

|                                                       | I <sub>SHDN_V5V</sub>     | V <sub>CHG</sub> =0V, V <sub>V5V</sub> =5V, EN=0,<br>V <sub>BAT</sub> =0V, OVP_SET=111, Null load.                                         |     | 15  |      | μΑ   |

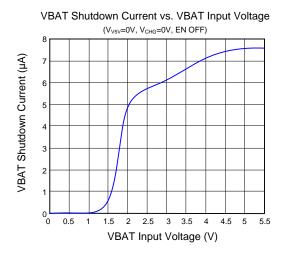

| Shutdown Current                                      | I <sub>SHDN_VBAT</sub>    | V <sub>CHG</sub> =0V, V <sub>V5V</sub> =0V, EN=0,<br>V <sub>BAT</sub> =5V, OVP_SET=111, Null load.                                         |     | 8   |      | μΑ   |

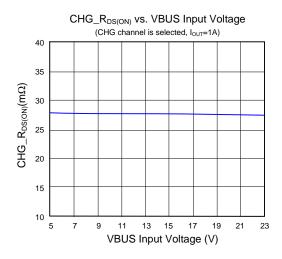

| On Resistance of HV<br>Power Path                     | R <sub>DS(ON)_HV</sub>    | HV channel is selected, Load is 1A                                                                                                         |     | 27  | 33   | mΩ   |

| Parameter                                           | Symbol                 | Test Conditions                                      | Min  | Тур  | Max  | Unit |

|-----------------------------------------------------|------------------------|------------------------------------------------------|------|------|------|------|

| On Resistance of 5V<br>Power Path                   | R <sub>DS(ON)_5V</sub> | 5V channel is selected, Load is 2A                   |      | 41   | 48   | mΩ   |

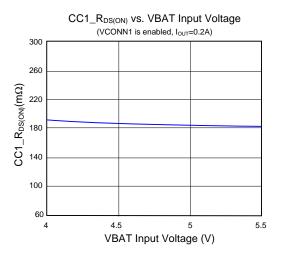

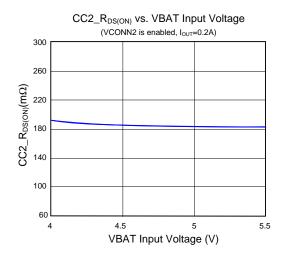

| On Resistance of V <sub>CONN</sub>                  | R <sub>DS(ON)_CC</sub> | VCONN is enabled, load=200mA                         |      | 170  | 210  | mΩ   |

| On Resistance of CC                                 |                        | CCx_BPS is enable, Load=1mA                          |      | 40   | 55   | Ω    |

| Bypass                                              | R <sub>DS(ON)_BP</sub> |                                                      |      | 40   | 33   | 52   |

| Reverse Block Threshold for HV                      | V <sub>TH_RCB_HV</sub> | VBUS - VCHG when HV channel is ON                    |      | 50   |      | mV   |

| Reverse Block Threshold for LV                      | V <sub>TH_RCB_5V</sub> | VBUS - V5V when 5V channel is ON                     |      | 50   |      | mV   |

| Reverse Block Response<br>Time                      | $t_{ m REV}$           |                                                      |      | 1    |      | μs   |

| Over Voltage Protection for V5V                     | V <sub>OVP_V5V</sub>   |                                                      | 5.7  | 6    | 6.3  | V    |

| Over Voltage Protection for VBAT                    | V <sub>OVP_CC</sub>    |                                                      | 5.7  | 6    | 6.3  | V    |

| Over Response Time                                  | tov                    | V5V rise from 5V to 7V                               |      | 100  |      | ns   |

|                                                     |                        | Default: OVP_SET=000                                 | 5.7  | 6    | 6.3  | V    |

|                                                     |                        | OVP_SET=001                                          | 8    | 8.4  | 8.8  | V    |

|                                                     |                        | OVP_SET=010                                          | 10.7 | 11.3 | 11.8 | V    |

| Over Voltage Protection for                         | ***                    | OVP_SET=011                                          | 11.7 | 12.3 | 12.9 | V    |

| HV                                                  | V <sub>OVP_HV</sub>    | OVP_SET=100                                          |      | 14.2 | 14.9 | V    |

|                                                     |                        | OVP_SET=101                                          |      | 17.9 | 18.8 | V    |

|                                                     |                        | OVP_SET=110                                          | 20.5 | 21.6 | 22.7 | V    |

|                                                     |                        | OVP_SET=111                                          | 22.5 | 23.7 | 24.9 | V    |

| Over Response Time of HV                            | _                      | OVP_SET=000, VBUS change from                        |      |      |      |      |

| Channel                                             | t <sub>OV_HV</sub>     | 5V to 8V                                             |      | 100  |      | ns   |

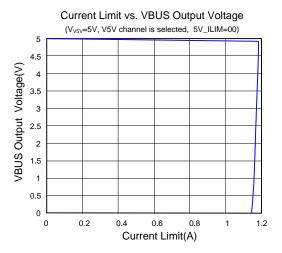

|                                                     |                        | Current limit control bit [00]                       | 1    | 1.25 | 1.5  | A    |

| Sourcing/Sinking Current<br>Limit Threshold for HV  | I                      | Current limit control bit [01]                       | 1.5  | 1.75 | 2    | A    |

| Power Path                                          | $I_{LIM\_HV}$          | Default: Current limit control bit [10]              | 3    | 3.3  | 3.6  | A    |

|                                                     |                        | Current limit control bit [11]                       | 5    | 5.5  | 6    | A    |

|                                                     |                        | Current limit control bit [00]                       | 1    | 1.25 | 1.5  | A    |

| Sourcing Current Limit                              | T                      | Current limit control bit [01]                       | 1.5  | 1.75 | 2    | A    |

| Threshold for 5V Power Path                         | I <sub>LIM_5V</sub>    | Current limit control bit [10]                       | 2    | 2.25 | 2.5  | A    |

|                                                     |                        | Default: Current limit control bit [11]              | 3    | 3.3  | 3.6  | A    |

|                                                     |                        | Current limit response time control bit[00]          |      | 1    |      | ms   |

| Current Limit Response Time for HV Power Path/      |                        | Default: Current limit response time control bit[01] |      | 10   |      | ms   |

| ALERT_L Response Time for Over Current Protection   | t <sub>OC</sub>        | Current limit response time control bit[10]          |      | 50   |      | ms   |

|                                                     |                        | Current limit response time control bit[11]          |      | 100  |      | ms   |

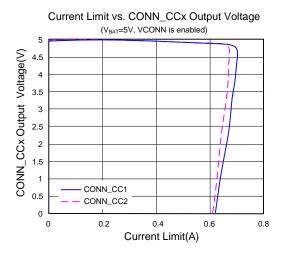

| V <sub>CONN</sub> Current Limit<br>Threshold        | I <sub>VCONN</sub>     | VBAT=5V, VCONNx=1                                    | 600  | 660  | 720  | mA   |

| Current Limit Response<br>Time of V <sub>CONN</sub> | t <sub>VCONN_OC</sub>  |                                                      |      | 4    |      | μs   |

| Parameter                            |                       | Symbol                  | Test Conditions                                  | Min  | Тур  | Max  | Unit   |

|--------------------------------------|-----------------------|-------------------------|--------------------------------------------------|------|------|------|--------|

| Thermal Shutdown                     |                       | $T_{SD}$                |                                                  |      | 150  |      | °C     |

| Temperature                          |                       | 130                     |                                                  |      | 100  |      |        |

| Thermal Shut                         | down                  | $T_{HYS}$               |                                                  |      | 15   |      | °C     |

| Hysteresis Transition S <sub>1</sub> | i - 4i                |                         |                                                  |      |      |      |        |

| Positive Slew                        |                       |                         |                                                  |      |      |      |        |

| VBUS When                            |                       | V <sub>SLEW_POS</sub>   |                                                  |      | 2    |      | V/ms   |

| Transition                           | Chaimei               | V SLEW_POS              |                                                  |      |      |      | V/1113 |

| Negative Slev                        | v Rate of             |                         |                                                  |      |      |      |        |

| VBUS When                            |                       | V <sub>SLEW NEG</sub>   |                                                  |      | -2   |      | V/ms   |

| Transition                           |                       |                         |                                                  |      |      |      |        |

| Rise Time of                         | V <sub>CONN</sub>     | t <sub>rise_VCONN</sub> |                                                  |      | 250  |      | μs     |

| Transition Re                        | sponso Timo           | t-                      | Measure from I <sup>2</sup> C ACK to VOUT        |      | 1    |      | ms     |

| Transmon Re                          | sponse Time           | $t_{\mathrm{D}}$        | start rise or fall                               |      |      |      | 1115   |

|                                      |                       |                         | RDSG bit[00]                                     |      | 200  |      | Ω      |

| Discharge Re                         | sistance              | $R_{ m DSG}$            | RDSG bit[01]                                     |      | 400  |      | Ω      |

| Discharge Re                         | sistance              | TUSG                    | RDSG bit[10]                                     |      | 800  |      | Ω      |

|                                      |                       |                         | RDSG bit[11]                                     |      | 1600 |      | Ω      |

|                                      |                       |                         | TDSG bit[00]                                     |      | 50   |      | ms     |

| Discharge Tir                        | ne                    | $t_{ m DSG}$            | TDSG bit[01]                                     |      | 100  |      | ms     |

|                                      |                       | 4030                    | TDSG bit[10]                                     |      | 200  |      | ms     |

| E ( D. 1. C                          | T                     |                         | TDSG bit[11]                                     |      | 400  |      | ms     |

| Fast Role Swa<br>Threshold           |                       | $V_{FRS}$               | HV_DR=0, FRS_EN=1, VBUS drop, measure V5V - VBUS |      | 40   |      | mV     |

| Fast Role Swa<br>Threshold on        |                       | V <sub>FRS_CC</sub>     | HV_ER=0, FRS_EN=1, CC_FRS=1                      | 0.49 | 0.52 | 0.55 | V      |

|                                      |                       |                         | V5V =5V. From VOUT drop below                    |      |      |      |        |

| Fast Role Swa                        | ap Response           | $t_{FRS}$               | than 4.75V to VOUT back 4.75V                    |      |      | 100  | μs     |

|                                      | Logic-low             | V <sub>IL</sub>         | (Note 4)                                         |      |      | 0.4  | V      |

| EN/EN                                | Voltage               | ' IL                    | (1.000 1)                                        |      |      | 0.1  |        |

| Threshold                            | Logic-high<br>Voltage | $V_{IH}$                | (Note 4)                                         | 1.5  |      |      | V      |

| I <sup>2</sup> C Compati             |                       |                         |                                                  |      |      |      |        |

| Maximum Operating                    |                       |                         | (Note 4)                                         |      | 1    |      | MHz    |

| Frequency                            |                       |                         | (11010 4)                                        |      | 1    |      |        |

| SDA and SCL Input Logic              |                       | Logic_L                 | (Note 4)                                         |      |      | 0.4  | V      |

| Threshold                            |                       | Logic_H                 | (Note 4)                                         | 1.5  |      |      | V      |

| SDA Output I                         | Low Voltage           |                         | (Note 4)                                         |      |      | 0.4  | V      |

**Note 1**: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

Note 2:  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a high effective 4-layer thermal conductivity test board of JEDEC 51-7 thermal measurement standard.

**Note 3:** The device is not guaranteed to function outside its operating conditions.

Note 4: Guaranteed by design, not production test.

## **Typical Performance Characteristic**

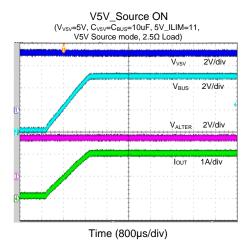

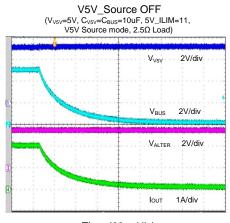

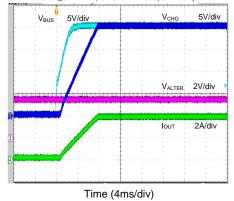

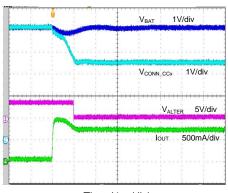

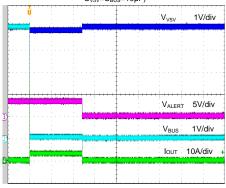

#### VBUS ON

$(V_{BUS}\!\!=\!\!20V,\,V_{V5V}\!\!=\!\!5V,\,C_{CHG}\!\!=\!\!C_{BUS}\!\!=\!\!10uF,\,CHG\_ILIM\!\!=\!\!11,\\OVP\_SET=\!111,\,CHG\,Sink\,mode,\,5\Omega\,Load)$

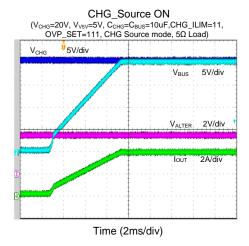

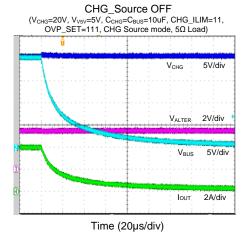

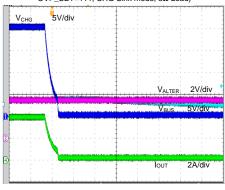

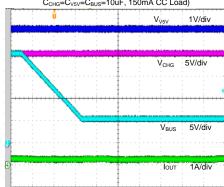

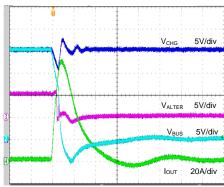

#### **VBUS OFF**

$(V_{BUS} = 20V, \ V_{V5V} = 5V, \ C_{CHG} = C_{BUS} = 10uF, \ CHG\_ILIM = 11, \\ OVP\_SET = 111, \ CHG \ Sink \ mode, \ 5\Omega \ Load)$

Time (4ms/div)

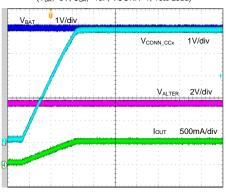

#### VCONN Switch ON

$(V_{BAT}=5V, C_{BAT}=1uF, VCONN=1, 10\Omega Load)$

Time (100µs/div)

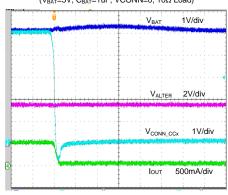

#### VCONN Switch OFF

$(V_{BAT}\!\!=\!\!5V,\,C_{BAT}\!\!=\!\!1uF,\,VCONN\!\!=\!\!0,\,10\Omega\;Load)$

Time (1µs/div)

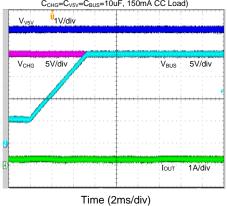

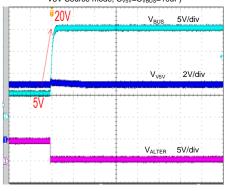

# $\begin{array}{c} Positive\ Voltage\ Transitions\\ (v_{\text{V5V}}=5\text{V},\ v_{\text{CHG}}=20\text{V},\ V_{\text{BUS}}=5\text{V}\rightarrow 20\text{V}, \text{OVP\_SET=111},\\ C_{\text{CHG}}=C_{\text{V5V}}=C_{\text{BUS}}=10\text{uF},\ 150\text{mA}\ CC\ Load) \end{array}$

Time (2ms/div)

## V5V Channel Over Current Response (V<sub>V5V</sub>=5V, V5V Source mode, 5V\_ILIM=00, OC\_DELAY=10, $3.5\Omega$ switch on)

Time (10ms/div)

## CHG Channel Over Current Response (V<sub>CHG</sub>=5V, CHG\_ILIM=00, DSG\_Time=00, OC\_DELAY=10, CHG Source mode, C<sub>CHG</sub>=C<sub>BUS</sub>=10uF, 3.5 $\Omega$ switch on)

Time (10ms/div)

#### VCONN Channel Over Current Response

(V<sub>BAT</sub>=5V, C<sub>BAT</sub>=1uF, Load=5 $\Omega$  ON)

Time (4µs/div)

### V5V Over Voltage Protection Response ( $V_{V5V}$ =5V, $V_{BUS}$ =5.0V $\rightarrow$ 20.0V, V5V Source mode, $C_{V5V}$ = $C_{VBUS}$ =10uF)

Time (10ms/div)

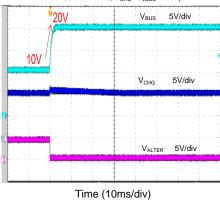

## CHG Over Voltage Protection Response ( $V_{VSV}$ =5V, $V_{CHG}$ =10V, OVP\_SET=010, $V_{BUS}$ =10.0V $\rightarrow$ 20.0V, CHG Source mode, $C_{CHG}$ = $C_{VBUS}$ =10uF)

VBAT Over Voltage Protection Response  $(V_{VSV}=V_{BAT}=SV,\ VCONN\ is\ enabled\ V_{CONN\_CC1/2}=5.0V\rightarrow20.0V,\ C_{BAT}=1uF)$

Time (10ms/div)

$\begin{array}{c} V5V\ Channel\ Short\ Response \\ (v_{V5V}=5V,\ V5V\ Source\ Mode,\ 5V\_ILIM=11,\ OC\_DELAY=10, \\ C_{V5V}=C_{BUS}=10\mu F) \end{array}$

Time (20ms/div)

#### CHG Channel Short Response

(V<sub>CHG</sub>=20V, CHG Source mode, EN=ON, C<sub>CHG</sub>=C<sub>BUS</sub>=10uF)

Time (2µs/div)

## V5V Channel Hot Plug Response ( $V_{V5V}$ =5V, V5V Souece mode, EN ON, $C_{V5V}$ = $C_{BUS}$ =10uF, Null load, $V_{BUS}$ =20V Plug In)

Time (10ms/div)

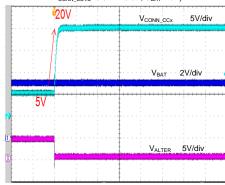

## CHG Channel Hot Plug Response ( $V_{\text{CHG}}$ =5V, CHG Source mode, EN ON, OVP\_SET=000, $C_{\text{CHG}}$ = $C_{\text{BUS}}$ =10uF, Null load, $V_{\text{BUS}}$ =20V Plug In)

Time (10ms/div)

Time (40µs/div)

## **Operation**

The SY6862B is a 2 to 1 power multiplexer switch providing programmable over current protection and over voltage protection for USB PD application. The SY6862B has a bi-directional high voltage power path that is capable of sinking or sourcing modes through an internal switch path designed to support USB-PD power up to 23V at 5A of current.

The SY6862B incorporates the back to back N-channel MOSFET on two low on resistance power path, so the IC could prevent the current-flow from OUT to IN when OUT being externally forced to a higher voltage than IN.

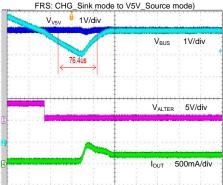

#### 1. I<sup>2</sup>C Compatible Interface

The SY6862B integrates an  $I^2C$  compatible interface. To ensure compatibility with a wide range of system processors, the  $I^2C$  interface supports clock speeds of up to 400kHz ("Fast-Mode") and uses standard  $I^2C$  commands. The SY6862B always operates as a slave device, and is addressed using a 7-bit slave address followed by an  $8^{th}$  bit, which indicates whether the transaction is a read-operation or a write-operation.

The I<sup>2</sup>C interface is fully functional after power supply is above UVLO threshold.

#### I<sup>2</sup>C Device Address

When communicating with multiple devices using the I<sup>2</sup>C interface, each device must have its own unique address so the host can distinguish between the devices. The most significant 5-bits of the device address is '10000' The 6th and 7th-bit device address of SY6862B is select by ADDR pin.

| RADDR             | Device Address |

|-------------------|----------------|

| ADDR short to GND | 1000000        |

| 44.2k             | 1000001        |

| 200k              | 1000010        |

| ADDR tie to VCC   | 1000011        |

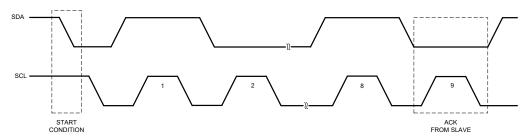

#### **START and STOP Conditions**

The START condition is a HIGH to LOW transition of the SDA line while SCL is HIGH. The STOP condition is a LOW to HIGH transition on the SDA line while SCL is HIGH. A STOP condition must be sent before each START condition. The I<sup>2</sup>C master always generates the START and STOP conditions.

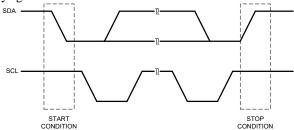

#### **Data Validity**

The data on the SDA line must be stable during the HIGH period of the SCL, unless generating a START or STOP condition. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW.

#### Acknowledge

Each address and data transmission uses 9-clock pulses. The ninth pulse is the acknowledge bit (ACK). After the

START condition, the master sends 7-slave address bits and an R/W bit during the next 8-clock pulses. During the ninth clock pulse, the device that recognizes its own address holds the data line low to acknowledge. The acknowledge bit is also used by both the master and the slave to acknowledge receipt of register addresses and data.

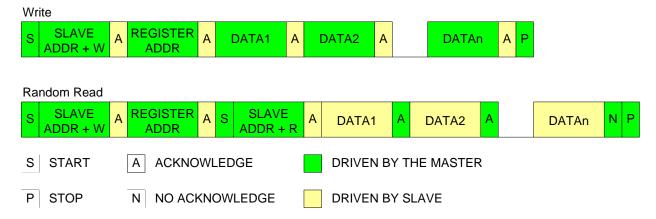

#### **Data Transactions**

All transactions start with a control byte sent from the I<sup>2</sup>C master device. The control byte begins with a START condition, followed by 7-bits of slave address followed by the R/W bit. The R/W bit is 0 for a write or 1 for a read. If any slave devices on the I<sup>2</sup>C bus recognize their address, they will acknowledge by pulling the SDA line low for the last clock cycle in the control byte. If no slaves exist at that address or are not ready to communicate, the data line will be 1, indicating a Not Acknowledge condition. Once the control byte is sent, and the SY6862B acknowledges it, the 2<sup>nd</sup> byte sent by the master must be a register address byte. The register address byte tells the SY6862B which register the master will write or read. Once the SY6862B receives a register address byte it responds with an acknowledgement. If a STOP condition is detected after the register address byte is received, the SY6862B takes no further action but storing the register address byte. The registers address byte auto increase when multiple date bytes are transited.

#### Register Map

Status register: 0x00

| Bit 7 |     |       |     |     |     |         | Bit 0   |

|-------|-----|-------|-----|-----|-----|---------|---------|

| OC_HV | RVS | OC_5V | OVP | FRS | TSD | Vsafe5V | Vsafe0V |

| R     | R   | R     | R   | R   | R   | R       | R       |

- Bit 7 OC\_HV: Over current indicator for High voltage power path. Load current exceeds the current limit value for longer than Toc. This bit will be set and power FET is turned off. This bit will be cleared when read if the error condition has been removed. This bit will cause the ALERT L pin to be asserted

- 1 = Load current exceeds the current limit value.

- 0 = High voltage power path not over current

- Bit 6 RVS: Reverse Block indicator for selected power path. When OUT is higher than IN 50mV, this bit will be set to 1. This bit will be cleared when read if the error condition has been removed. This bit will cause the ALERT\_L pin to be asserted

- High voltage path is enabled, source mode.

- 1 = VBUS > VCHG + 50mV

- 0 = Reverse block is not triggered

- High voltage path is enabled, sink mode.

- 1 = VCHG > VBUS + 50mV

- 0 = Reverse block is not triggered

- 5V voltage path is selected.

- 1 = VBUS > V5V + 50mV

- 0 = Reverse block is not triggered

- Bit 5 OC\_5V: Over current indicator for 5V voltage power path. This bit will be cleared when read if the error condition has been removed. This bit will cause the ALERT\_L pin to be asserted

- 1 = Load current exceeds the current limit value.

- 0 = 5V voltage power path not over current

- Bit 4 OVP: Over Voltage Protection for the selected channel. When 5V channel is selected, SY6862B will detect the VBUS voltage. Once VBUS is larger than 6V, this bit will be set to 1 and power FET will be turned off. When HV channel is selected, SY6862B will detect the VBUS voltage. Once the VBUS is larger than the presetting threshold by OVP\_SET, this bit will be set to 1 and power FET will be turned off.

- 1 = VBUS OVP is triggered

- 0 = OVP is not triggered

- Bit 3 FRS: Fast role swap is triggered. VBUS is lower than 4.75V. Fast role swap is triggered. HV channel is shutdown. V5V is turned on in 100us. This bit will be cleared when read. This bit will cause the ALERT L pin to be asserted.

- 1 = FRS is triggered

- 0 = FRS is not triggered

- Bit 2 TSD: Thermal shutdown indicator. When the junction temperature exceeds 150°C, this bit is set to 1. And Power FET is turned off. This bit will be cleared when read if the error condition has been removed. This bit will cause the ALERT\_L pin to be asserted.

- 1 = The junction temperature exceeds  $150^{\circ}$ C.

- 0 = The junction temperature is within safe range.

- Bit 1 Vsafe5V: Indicator VBUS is at Vsafe5V range.

- 1 = 4.0V < VBUS < 5.5V

- 0 = VBUS is out of Vsafe5V range.

- Bit 0 Vsafe0V: Indicator VBUS is at Vsafe0V range.

- 1 = VBUS < 0.8V

- 0 = VBUS > 0.8V

#### Control Register 1: 0x01

| Bit 7     |     |         |     |         |     |        | Bit 0    |

|-----------|-----|---------|-----|---------|-----|--------|----------|

| Power_ENB | HV_ | HV_ILIM |     | 5V_ILIM |     | CH_SEL | Reserved |

| W/R       | W/R | W/R     | W/R | W/R     | W/R | W/R    | W/R      |

- Bit 7 Power\_ENB: Power delivery enable control. Default: 0. This bit will be set to 1 when OC\_HV, OVP, TSD is set to high.

- 1 = Both channel is turned off.

- 0 = High voltage channel or 5V voltage channel is active. Which channel is active decided by CH\_SEL.

- Bit 6-5 HV\_ILIM: High voltage power path source current limit control bit. Default: 10.

- 00 = 1.25A

- 01 = 1.75A

- 10 = 3.3A

- 11 = 5.5A

- Bit 4-3 5V\_ILIM: 5V voltage power path source current limit control bit. Default: 11.

- 00 = 1.25A

- 01 = 1.75A

- 10 = 2.25A

- 11 = 3.3A

- Bit 2 HV\_DR: High voltage path power delivery direction control. Default: 0.

- 1 = Source mode, Delivery power from VCHG to VBUS.

- 0 = Sink mode, Delivery power from VBUS to VCHG

- Bit 1 CH\_SEL: Channel selection bit. Default: 1.

- 1 = High voltage power path is selected.

- 0 = 5V voltage power path is selected.

- Bit 0 Reserved.

Control Register 2: 0x02

| Bit 7 |                   |     |     |      |      |      |      |  |  |  |

|-------|-------------------|-----|-----|------|------|------|------|--|--|--|

| OC_D  | OC_DELAY DSG_TIME |     |     | DSG_ | _RON | SDSG | FDSG |  |  |  |

| W/R   | W/R               | W/R | W/R | W/R  | W/R  | W/R  | W/R  |  |  |  |

Bit 7-6 OC\_DELAY: Program the over current response delay time. Default: 01.

00: 1ms

01: 10ms

10: 50ms

11: 100ms

Bit 5-4 DSG\_TIME: Program the discharge time. Default: 10.

00: 50ms

01: 100ms

10: 200ms

11: 400ms

Bit 3-2 DSG\_RON: Program the discharge resister. Default: 00.

$00:200\Omega$

$01:400\Omega$

10:  $800\Omega$

11:  $1600\Omega$

Bit 1 SDSG: Smart Discharge mode, Default: 1.

0: Discharge FET ON/OFF is only controlled by FDSG bit.

1: SY6862B worked at smart discharge function.

Bit 0 FDSG: Force Discharge mode, Default: 0.

0: Discharge FET is controlled by SDSG.

1: Discharge FET is forced turned on.

#### Control Register 3: 0x03

| Bit 7 | ,   |         |     |          |          |          | Bit 0   |

|-------|-----|---------|-----|----------|----------|----------|---------|

| BUSY  |     | OVP_SET |     | RVS_MASK | Reserved | Reserved | RST_REG |

| R     | W/R | W/R     | W/R | W/R      | W/R      | W/R      | W/R     |

BUSY: I<sup>2</sup>C busy indicate. When SY6862B is in channel transition state or count discharge time period, this Bit 7 bit will be set to 1. After this channel transition or discharge timer expired, the bit will set to 0 automatically.

$1 = I^2C$  busy, the command of  $I^2C$  will be ignored

$0 = \text{Receive I}^2\text{C}$  command normally

- Bit 6-4 OVP\_SET: Over voltage protection setting for HV channel. Default: 000

- 000: 5V power profile application, typical OVP value is 6V

- 001: 7V power profile application, typical OVP value is 8.4V

- 010: 9V power profile application, typical OVP value is 11.1V

- 011: 10V power profile application, typical OVP value is 12.1V

- 100: 12V power profile application, typical OVP value is 14.2V

- 101: 15V power profile application, typical OVP value is 17.9V

- 110: 18V power profile application, typical OVP value is 21.6V

- 111: 20V power profile application, typical OVP value is 23.7V

- Bit 3 RVS\_MASK: LV and HV reverse blocking protection interrupt mask. Default:0.

- 1: ALERT\_L is not response when LV or HV reverse blocking protection is triggered.

- 0: ALERT\_L is pulled low immediately when LV or HV reverse blocking protection is triggered.

- Bit 0 RST\_REG: Reset all I<sup>2</sup>C registers to default value

- 1: Reset all I<sup>2</sup>C registers to default value

- 0: Default value. No action

#### Control Register 4: 0x04

| Bit 7   |         |        |        |          |          |        | Bit 0    |

|---------|---------|--------|--------|----------|----------|--------|----------|

| CC1_BPS | CC2_BPS | VCONN1 | VCONN2 | VBAT_OVP | VCONN_OC | CC_FRS | Reserved |

| W/R     | W/R     | W/R    | W/R    | R        | R        | W/R    | W/R      |

- Bit 7 CC1\_BPS: Combine HOST\_CC1 to CONN\_CC1. Before Combine HOST\_CC1 to CONN\_CC1, the exposed Rd should be removed first. Default: 0.

- 1 = HOST\_CC1 and CONN\_CC1 are internal connected.

- 0 = HOST\_CCx and CONN\_CCx are isolated.

- Bit 6 CC2\_BPS: Combine HOST\_CC2 to CONN\_CC2. Before Combine HOST\_CC2 to CONN\_CC2, the exposed Rd should be removed first. Default: 0.

- 1 = HOST CC2 and CONN CC2 are internal connected.

- 0 = HOST CCx and CONN CCx are isolated.

- Bit 5 VCONN1: VCONN select bit. Default: 0.

- 1 = Select CONN\_CC1 as VCONN. CC1\_BPS is set to 0. CONN\_CC1 is connected to VBAT.

- 0 = CONN CC1 is not selected as VCONN.

- Bit 4 VCONN2: VCONN select bit. Default: 0.

- 1 = Select CONN\_CC2 as VCONN. CC2\_BPS is set to 0. CONN\_CC2 is connected to VBAT.

- $0 = CONN_CC2$  is not selected as VCONN.

- Bit 3 VBAT\_OVP: When VBAT is over 6V, VBAT\_OVP is set to 1. This bit will be cleared when read if the error condition has been removed. This bit will cause the ALERT\_L pin to be asserted

- 1 = VBAT OVP triggered

- $0 = VBAT_OVP$  not triggered

- Bit 2 VCONN\_OC: VCONN channel over current indication: Once load current is larger ICONN, the VCONN channel will turned off and the VCONNx bit is set to 0. This bit will be cleared when read if the error condition has been removed. This bit will cause the ALERT\_L pin to be asserted

- 1 = Over current on VCONN.

- 0 = Load is normal on VCONN.

- Bit 1 CC\_FRS: Fast Role Swap signal detect enable pin. Default: 0.

- 0: Fast Role Swap signal detection is enabled on CC pin

- 1: Fast Role Swap signal detection is not enabled. FRS is controlled by FRS\_EN and VBUS detection.

#### 2. Channel transition sequence

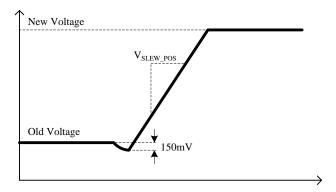

The SY6862B integrated smooth channel transition control to match USB PD specification. Positive transition sequence is shown below. The voltage ramp will remain monotonic until the voltage reaches final voltage. At the onset of transition, old voltage should not drop more than 150mV. And during transition, load power consumption shall not over 150mW.

**Figure 3. Positive Transition**

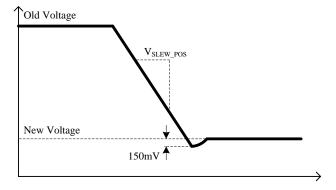

The waveform for a negative voltage transition is shown as Fig. 4. The voltage ramp will remain monotonic until the voltage reaches the final voltage. At the onset of transition, old voltage should not drop more than 150mV. And during transition, load power consumption shall not over 150mW.

Figure 4. Negative Transition

#### 3. EN Control

The EN pin is used for enabling or disabling power segment of the device. When VCHG, V5V or VBAT is presented and EN is high, the power FET can be configured on and off by I<sup>2</sup>C, Otherwise the power FET is keeps off. In order to wake up a dead battery system, Once VCHG, V5V and VBAT are under UVLO and VBUS is at Vsafe5V, EN state will be ignored. HV channel will be turned on to deliver power to the dead battery system.

#### 4. Dead Battery Wake up

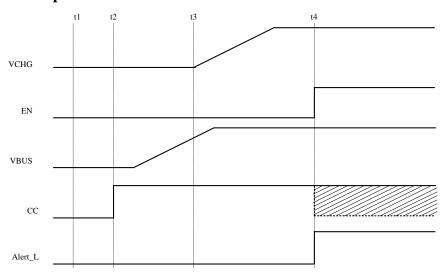

Figure 5. Dead Battery Mode Timing Diagram

- t1: System is under dead battery condition; the CCs expose an Rd resister to GND as a UFP.

- t2: A USB type C DFP is connected. Rd is detected by the DFP.

- t3: VBUS is powered on by DFP. Once VBUS is higher than 4.5V, HV power path turned on. VCHG starts rise up.

- t4: System logic circuit is supplied by VCHG; EN may be set high after VCHG is high. And once the EN is high, CC pins is connected HOST\_CC pins. The CC state is controlled by Host. Alert\_L is pulled high.

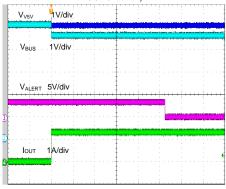

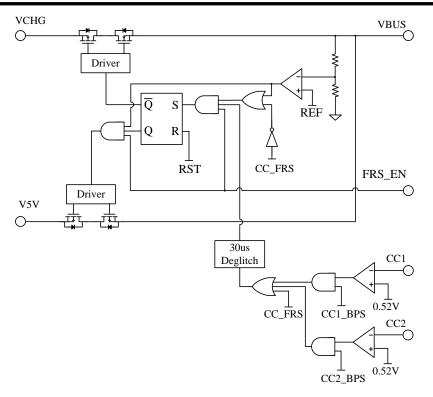

#### 5. Fast Role Swap

The SY6862B integrates fast role swap function which can support swap from UFP to DFP in  $150\mu s$  to meet USB PD 3.0 specification. Set CC\_FRS to 0, and CCx\_BPS to 1, when CCx is lower than 0.52V for longer than  $30\mu s$ , VCHG channel stop sink current. Meanwhile VBUS will decrease as DFP not provide power anymore. When VBUS drop below than V5V-40mV, the V5V channel will be turned on immediately and pull VBUS above 4.75V within  $100\mu s$ .

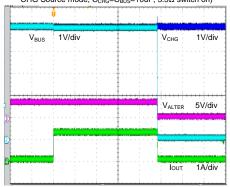

If CC\_FRS is set to 1, the SY6862B won't detect CC voltage. During VCHG channel working at sink mode, when VBUS drop below V5V-40mV, VCHG channel is shut down and V5V channel turned on within 100µs.

Figure 6. Fast Role Swap Block Diagram

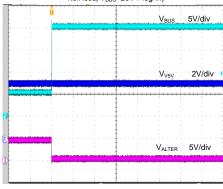

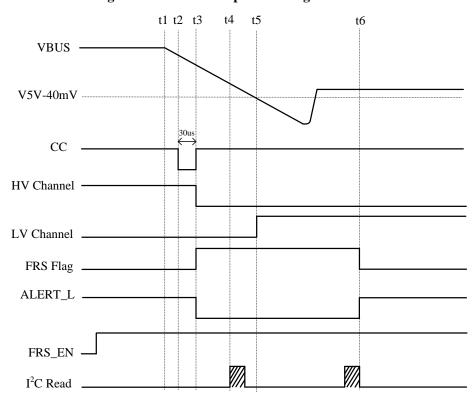

Figure 7. Timing Diagram on CC\_FRS=0

- t1: VBUS power supply is detached.

- t2: Hub sends FRS signal on CC to pull low.

- t3: CC deglitch time is done, HV sink channel is turned off, Fast Role Swap is detected and ALERT\_L is pulled low.

- t4: I2C read the FRS bit. ALERT\_L keeps low and FRS flag keeps high unless FRS status is removed

- (1. FRS\_EN disable, 2. CC\_FRS disable, 3. LV channel has already turned on).

- t5: When VBUS drops below than V5V-40mV, V5V channel is enabling to drive VBUS

- t6: FRS flag is pulled down and ALERT\_L is pulled high after I<sup>2</sup>C read.

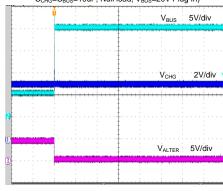

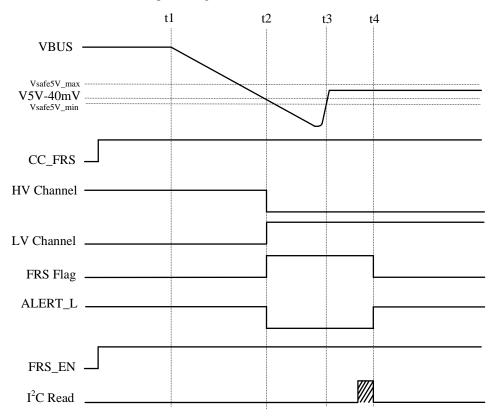

Figure 8. Timing Diagram on CC\_FRS=1

- t1: VBUS power supply is detached.

- t2: When VBUS drops below than V5V-40mV, HV sink channel is turned off, then V5V channel is enabling to drive

- VBUS. Fast Role Swap is detected and ALERT\_L is pulled low.(This situation is applied for CC\_FRS is disabled).

- t3: VBUS back to Vsafe5V range. ALERT\_L keeps low and FRS flag keeps high unless FRS has been read.

- t4: FRS flag is pulled down and ALERT\_L is pulled high after I<sup>2</sup>C read.

#### 6. Smart Discharge Function

The SY6862B integrated smart discharge function. If SDSG is set to 1 and SY6862B works at source mode, VBUS will be auto discharge when UVLO, Channel shutdown, OCP, OVP, TSD. The discharge time is set by writing DSG\_TIME[1:0]. The  $R_{DS(ON)}$  of discharge FET is set by writing DSG\_RON[1:0].

The SY6862B also can be worked at force discharge mode for VBUS. Once SDSG is set to 0, the discharge FET ON/OFF is only controlled by FDSG. When FDSG is 1, the discharge FET is on. When FDSG is 0, the discharge FET is off. The discharge FET  $R_{DS(ON)}$  of discharge FET is set by writing DSG\_RON[1:0].

#### 7. I<sup>2</sup>C Busy

During channel transition or counting discharge time, the BUSY bit will be set high. When the busy bit is high, the I<sup>2</sup>C command will be ignored.

#### **8. Over Current Protection**

The SY6862B supports Current limit programming by I<sup>2</sup>C control at CHG/V5V power path. And the current limit of VCONN path is fixed at 660mA. The current limit of CHG/V5V channel is set by writing code to control register 1(0x01).

Bit 6-5 is CHG power path source and sink current limit control bit(Default:10).

00 = 1.25A

01 = 1.75A

10 = 3.3A

11 = 5.5A

Bit 4-3 is V5V power path source current limit control bit(Default:11).

00 = 1.25A

01 = 1.75A

10 = 2.25A

11 = 3.3A.

For V5V or VCONN channel, once the load current intends to exceed the current limit threshold, the gate of the pass switch is modulated to achieve constant output current. If the over current condition persists for a long time, the junction temperature may exceed 150°C, and over-temperature protection will shut down the part. Once the chip temperature drops below 130°C, the part will restart.

For CHG channel, once load current is over current limit threshold, the power path would be shut down after  $t_{OC}$ . Furthermore, once load current is greater than 2.7 times current limit threshold, the power path would be shut down directly.

#### 9. Fault Flag(ALERT\_L)

The ALERT\_L pin is an open drain output to signal interrupts. The ALERT\_L output is asserted (active low) when the over current of LV/HV channel continues to exceed  $t_{OC}$ . And the ALERT\_L output is asserted directly when thermal shutdown protection, over voltage protection, reverse blocking, or fast role swap is triggered. The output remains asserted until all registers of the device are read by  $I^2C$  control.

#### 10. Over Voltage Protection

The SY6862B integrated over voltage protection for V5V and VBAT pin. When V5V exceeds 6V (typ.), the power FET of LV channel will be turned off to protect low voltage input stage during reverse block application, and ALERT\_L is pulled low to indicate fault condition. When VBAT exceeds 6V(typ.), the VCONN1/2 switch will be disabled to protect low voltage input stage during reverse block application on CONN\_CC1/2.

The SY6862B integrated over voltage protection for VCHG and VBUS pin for the HV power path, the power FET of HV channel will be turned off rapidly when VCHG or VBUS exceeds OVP\_SET value.

#### 11. Reverse Block Function

The SY6862B integrates reverse block function on CHG power path and V5V power path. Once the deviation voltage of OUT-IN exceeds 50mV, the reverse block function is triggered. The power FET will be shutdown in 1us block the reverse current flow from OUT to IN.

#### 12. CC Line Capacitance

USB PD has a specification for the total amount of capacitance on CC lines, and the specification from section 5.8.6 of the USB PD Specification is given below in Table 1.

| Name      | Description             | Min | Max | Unit | Comment                                                                                           |

|-----------|-------------------------|-----|-----|------|---------------------------------------------------------------------------------------------------|

| cReceiver | CC receiver capacitance | 200 | 600 | pF   | The DFP or UFP system shall have capacitance within this range when not transmitting on the line. |

Table 1. USB PD cReceiver Specification

A 330pF ceramic capacitor is strongly recommended to be placed on the CC line.

#### 13. CC Dead Battery Mode

The SY6862B exposes a 5.1k resister to GND on CONN\_CCx when the device is unpowered. Once the power adaptor detects the pull-down resistor, it would apply 5V on the VBUS pin. As VBUS is exceeds UVLO, the CHG path would be turned on, thus the system is powered and could awake up from dead battery condition.

After system is wake up, PD controller could write CCx\_BPS to 1 to take over CC line control for higher power delivery. Pls note once HOST\_CCx is bypass to CONN\_CCx, the pull down resister is removed, PD controller should also exposed a 5.1k resistor to keep VBUS present. Table 2 shows the CONN\_CCx connection state results.

| CCx_BPS | VCONNx | CONN_CCx STATE          |

|---------|--------|-------------------------|

| 0       | 0      | Expose a Rd resistor    |

| 0       | 1      | Connect to the VBAT     |

| 1       | 0      | Connect to the Host_CCx |

| 1       | 1      | Connect to the VBAT     |

Table2. CONN\_CCx Connection State

#### 14. V5V Capacitor

In order to prevent the input voltage drooping during hot-plug events, a  $1\mu F$  ceramic capacitors from V5V to GND is strongly recommended. However, higher capacitor values could reduce the voltage droop on the V5V further. Furthermore, a VBUS short will cause ringing on the input without the input capacitor. It could destroy the internal circuitry when the input transient exceeds the absolute maximum supply voltage even for a short duration.

#### 15. VBUS Capacitor

A  $1\mu F$  ceramic capacitor is recommended to be placed close to the IC and output connector to reduce voltage drop during load transient. Higher values of ceramic capacitor can be used for further reducing the drop during high current application.

There would be a high voltage spike during an un-expected high voltage plug into USB type C port. It is strongly recommended add a TVS of SYS12V20SLC on VBUS to GND to clamp the voltage spike lower than absolute voltage rating.

During high voltage application, VBUS may have a negative voltage as the resonance of leakage-inductance of cable wire and output cap. This negative voltage may lead IC work abnormal. It is recommended to add a schottky diode to clamp VBUS at a safe voltage range.

#### 16. VCHG Capacitor

A  $10\mu F$  or larger input ceramic capacitor is strongly recommended to be placed close to the IC. Furthermore, a VBUS short will cause ringing on the VCHG without the VCHG capacitor. It could destroy the internal circuitry when the VCHG transient exceeds the absolute maximum voltage rating even for a short duration.

The USB PD 3.0 specification defines sink bulk capacitance which shall not exceed 100µF so that the transient charging, or discharging, of the total bulk capacitance on VBUS can be accounted for during voltage transitions.

#### 17. Signal Integrity

A  $100\Omega$  resister from SDA/SCL to J1/J2 is recommended to avoid potential signal integrity risk.

#### 18. PCB Layout Guide

For best performance of the SY6862B, the following guidelines must be strictly followed:

- 1. Keep all VBUS traces as short and wide as possible and use at least 2-ounce copper for all VBUS traces.

- 2. Locate the output capacitor as close to the connectors as possible to lower impedance (mainly inductance) between the port and the capacitor and improve transient performance.

- 3. Input and output capacitors should be placed closed to the IC and connected to ground plane to reduce noise coupling.

- 4. The VBUS, CONN\_CC1 and CONN\_CC2 pins are exposed externally and adding a TVS each is necessary to prevent surge voltage.

**Fig.9 PCB Layout Suggestion**

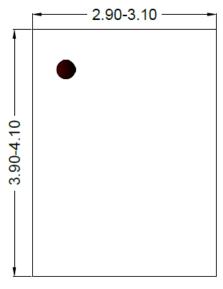

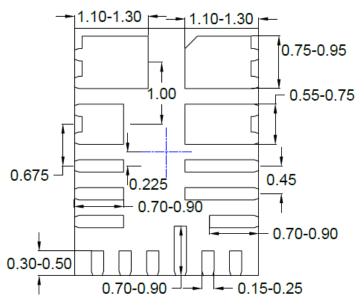

## QFN3×4-16 Package Outline Drawing

**Top View**

**Bottom View**

(Reference only)

Notes: 1, All dimension in millimeter and exclude mold flash & metal burr. 2, Center of PCB refers the chip body Center.

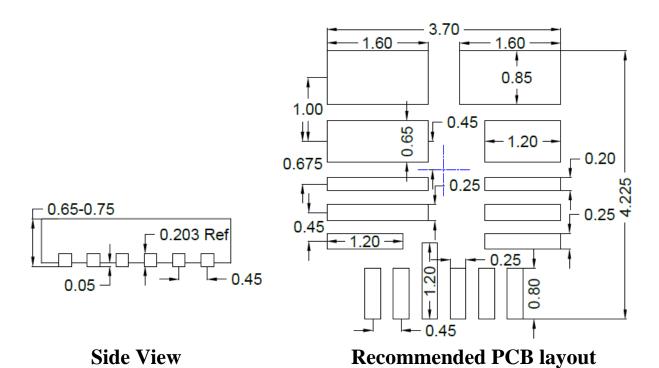

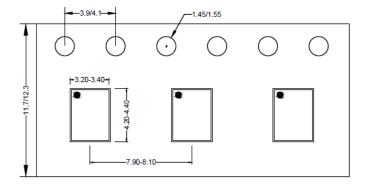

## **Taping & Reel Specification**

### 1. Taping orientation

QFN3×4

Feeding direction -

## 2. Carrier Tape & Reel specification for packages

| Package<br>type | Tape width (mm) | Pocket pitch(mm) | Reel size<br>(Inch) | Trailer<br>length(mm) | Leader length<br>(mm) | Qty per<br>reel |

|-----------------|-----------------|------------------|---------------------|-----------------------|-----------------------|-----------------|

| QFN3×4          | 12              | 8                | 13"                 | 400                   | 400                   | 5000            |

## 3. Others: NA

## **Revision History**

The revision history provided is for informational purpose only and is believed to be accurate, however, not warranted. Please make sure that you have the latest revision.

| Date         | Revision      | Change                                                                                                                                            |  |

|--------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Mar.22, 2022 | Revision 1.0  | 1. Update the ON resistance (page 5~6);                                                                                                           |  |

|              |               | 2. Add Max. value of "On Resistance of CC Bypass" (page 6);                                                                                       |  |

|              |               | 3. Add Note 4 in EC table (page 7).                                                                                                               |  |

| Dec.23, 2021 | Revision 0.9B | 1. Update the schematic diagram (page 1);                                                                                                         |  |

|              |               | 2. Update the PCB Layout Guide (page 26)                                                                                                          |  |

| Mar.18, 2021 | Revision 0.9A | Delete "At sink mode, VCHG will be auto discharged when UVLO, Channel shutdown, OCP, OVP, TSD." in Smart Discharge Function Description. (page23) |  |

| Jan.21, 2021 | Revision 0.9  | Initial Release                                                                                                                                   |  |

#### IMPORTANT NOTICE

- 1. **Right to make changes.** Silergy and its subsidiaries (hereafter Silergy) reserve the right to change any information published in this document, including but not limited to circuitry, specification and/or product design, manufacturing or descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to Silergy's standard terms and conditions of sale.

- 2. Applications. Application examples that are described herein for any of these products are for illustrative purposes only. Silergy makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Buyers are responsible for the design and operation of their applications and products using Silergy products. Silergy or its subsidiaries assume no liability for any application assistance or designs of customer products. It is customer's sole responsibility to determine whether the Silergy product is suitable and fit for the customer's applications and products planned. To minimize the risks associated with customer's products and applications, customer should provide adequate design and operating safeguards. Customer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Silergy assumes no liability related to any default, damage, costs or problem in the customer's applications or products, or the application or use by customer's third-party buyers. Customer will fully indemnify Silergy, its subsidiaries, and their representatives against any damages arising out of the use of any Silergy components in safety-critical applications. It is also buyers' sole responsibility to warrant and guarantee that any intellectual property rights of a third party are not infringed upon when integrating Silergy products into any application. Silergy assumes no responsibility for any said applications or for any use of any circuitry other than circuitry entirely embodied in a Silergy product.

- 3. **Limited warranty and liability.** Information furnished by Silergy in this document is believed to be accurate and reliable. However, Silergy makes no representation or warranty, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. In no event shall Silergy be liable for any indirect, incidental, punitive, special or consequential damages, including but not limited to lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges, whether or not such damages are based on tort or negligence, warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, Silergy' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Standard Terms and Conditions of Sale of Silergy.

- 4. **Suitability for use.** Customer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of Silergy components in its applications, notwithstanding any applications-related information or support that may be provided by Silergy. Silergy products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Silergy product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Silergy assumes no liability for inclusion and/or use of Silergy products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

- 5. **Terms and conditions of commercial sale**. Silergy products are sold subject to the standard terms and conditions of commercial sale, as published at http://www.silergy.com/stdterms, unless otherwise agreed in a valid written individual agreement specifically agreed to in writing by an authorized officer of Silergy. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Silergy hereby expressly objects to and denies the application of any customer's general terms and conditions with regard to the purchase of Silergy products by the customer.

- 6. No offer to sell or license. Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights. Silergy makes no representation or warranty that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right. Information published by Silergy regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from Silergy under the patents or other intellectual property of Silergy.

For more information, please visit: www.silergy.com

©2022 Silergy Corp.

All Rights Reserved.