### **General Description**

SY52257 is a high-performance synchronous rectifier which contains controller and MOSFET devices. This solution not only directly reduces power dissipation of the rectifier but also indirectly reduces primary-side losses, due to compounding of efficiency gains. The DRAIN pin of SY52257 can support 60V voltage stress.

SY52257 will achieve ultra-low power consumption when the circuit operates in no load.

The SY52257 is available in a compact SOT335 package.

### Features

- Smart Turn off Technology

- Secondary-side Synchronous Rectifier Optimized for 5V~12V Systems

- Suitable for Discontinuous Mode (DCM), Critical Conduction Mode (CRM)

- Suitable for Primary Side Regulation(PSR), Secondary Side Regulation (SSR)

- RoHS Compliant and Halogen Free

- Compact Package: SOT335

### Applications

- AC/DC Adapters

- Battery Chargers

- Consumer Electronics

- Auxiliary Power Supplies

| Recommended operating output power |                      |                       |

|------------------------------------|----------------------|-----------------------|

| Products                           | V <sub>OUT</sub> =5V | V <sub>OUT</sub> =12V |

| SY52257                            | 2.1A                 | 2A                    |

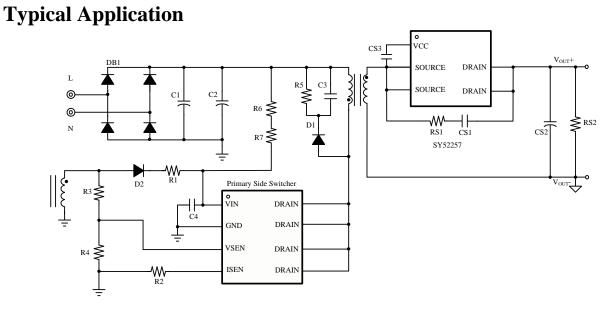

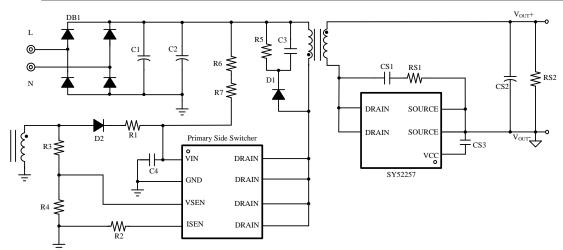

Fig.1 Typical Application Circuit in High Side

Fig.2 Typical Application Circuit in Low Side

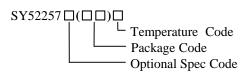

### **Ordering Information**

| Ordering Number | Package | Top Mark |  |

|-----------------|---------|----------|--|

| SY52257AZC      | SOT335  | CMZxyz   |  |

|                 |         |          |  |

x=year code, y=week code, z= lot number code

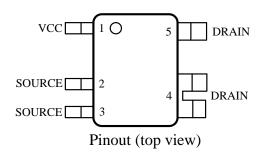

### Pinout (top view)

| Pin number | Pin Name | Pin Description                                                                       |

|------------|----------|---------------------------------------------------------------------------------------|

| 1          | VCC      | Power supply pin. This pin connects a $0.1 \mu$ F or larger ceramic bypass capacitor. |

| 2,3        | SOURCE   | SOURCE of the internal power MOSFET.                                                  |

| 4,5        | DRAIN    | DRAIN of the internal power MOSFET.                                                   |

## Absolute Maximum Ratings (Note 1)

| VCC                                   | 0.3V~16V      |

|---------------------------------------|---------------|

| DRAIN                                 |               |

| I <sub>VCC</sub>                      | 20mA          |

| Power Dissipation, @ TA = 25°C SOT335 | 0.67W         |

| Package Thermal Resistance (Note 2)   |               |

| SOT335, θ <sub>JA</sub>               |               |

| SOT335, θ <sub>JC</sub>               | 55°C/W        |

| Junction Temperature Range            | 45°C to 150°C |

| Lead Temperature (Soldering, 10 sec.) | 260°C         |

| Storage Temperature Range             | 65°C to 150°C |

## **Recommended Operating Conditions**

| Junction Temperature Range | 40°C to 125°C |

|----------------------------|---------------|

|                            |               |

| Ambient Temperature Range  | 40°C to 105°C |

### **Electrical Characteristics**

$(V_{VCC} = 10V, T_A = 25^{\circ}C \text{ unless otherwise specified})$

| Parameter                      | Symbol                  | Test Conditions                            | Min  | Тур  | Max  | Unit |

|--------------------------------|-------------------------|--------------------------------------------|------|------|------|------|

| Power Supply Section           |                         | ·                                          |      |      |      |      |

| VCC Turn-on Threshold          | V <sub>VCC_ON</sub>     |                                            | 3.6  | 3.75 | 3.9  | V    |

| Hysteresis Voltage             | V <sub>HYSTERESIS</sub> |                                            | 75   | 115  | 155  | mV   |

| Quiescent Current              |                         |                                            |      | 160  | 200  | μA   |

| Threshold Section              |                         | ·                                          |      |      |      |      |

| On_threshold                   |                         |                                            | -240 | -190 | -140 | mV   |

| Blanking Time section          |                         |                                            |      |      |      |      |

| Min Ton                        | T <sub>ON_BLANK</sub>   |                                            | 800  | 1200 | 1600 | ns   |

| Min Toff                       | T <sub>OFF_BLANK</sub>  |                                            | 1800 | 2200 | 2600 | ns   |

| MOSFET Section                 |                         |                                            |      |      |      |      |

| Mosfet Break Down Voltage      | V <sub>DSS(BR)</sub>    | V <sub>GS</sub> =0V,I <sub>D</sub> =0.25mA | 60   |      |      | V    |

| Mosfet On-state Resistor       | R <sub>DS(ON)</sub>     | V <sub>GS</sub> =10V,I <sub>D</sub> =5A    |      | 16   |      | mΩ   |

| Thermal Section                | •                       |                                            |      | •    | •    | •    |

| Thermal Shutdown Temperature   | T <sub>SD</sub>         |                                            |      | 150  |      | °C   |

| Hysteresis to Resume Operating | T <sub>OTP_HYS</sub>    |                                            |      | 20   |      | °C   |

**Note 1**: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2:  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

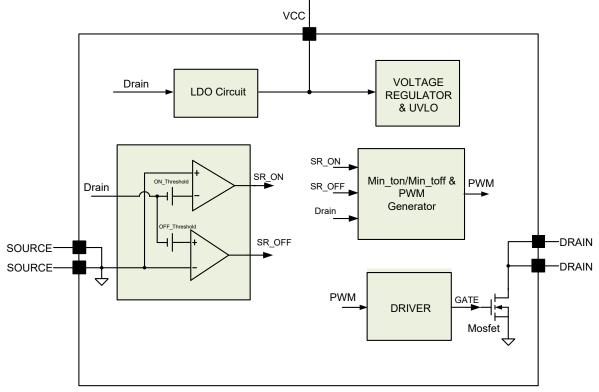

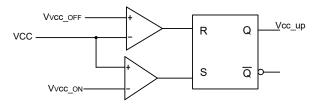

### **Block Diagram**

Fig.3 Block diagram

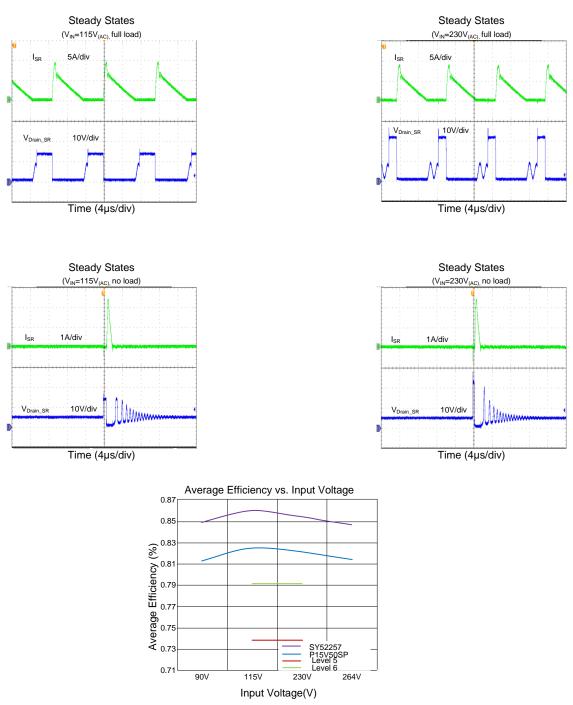

# **Typical Performance Characteristics**

(Test condition: input voltage: 90Vac; output spec: 5Vdc\_2.1A; Ambient temperature: 25±5 °C; Ambient humidity: 65±25 %.)

Fig.4 Average Efficiency Curve

### Description

### <u>SR Turn On</u>

When a negative voltage lower than on threshold  $V_{ON\_THR}$  is sensed on the DSEN pin, the driver logic turns up, then after a delay time, the GATE is pulled high.

#### Accuracy Zero Current Turn off Strategy

The initial turn off threshold  $V_{OFF\_INITIAL}$  of SR switcher is -30mV (typical value). When the Drain voltage on the SR is higher than the turn off threshold, the SR would turn off after a delay time.

SY52257 adopts a smart control strategy to achieve SR accuracy zero current turn off by compensating the off threshold each switching period, which also make SR operating in high efficiency and reliability.

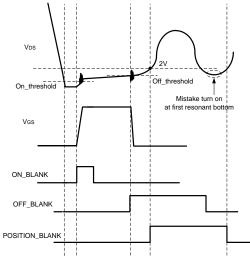

### Min Ton & Min Toff

After switch-on of the SY52257, the input signal on the DRAIN pin is blanked during the on blanking time  $T_{ON\_BLANK}$ . This action eliminates false switch-off due to high frequency ringing at the start of the secondary stroke. (See ON\_BLANK in Fig.5).

After switch-off of the SY52257, the input signal on the DRAIN pin is blanked during the off blanking time. This action eliminates false switch-on due to high frequency ringing at the start of the secondary stroke. (See OFF\_BLANK in Fig.5)

Fig.5 timing diagram of Min\_ton & Min\_toff

To prevent SR false turn on after resonant period which caused by primary magnetic inductor and primary equivalent cap, the off blanking time is not enough to accomplish. The position blanking time T<sub>POSITION\_BLANK</sub> can work out. (See POSITION\_BLANK in Fig.5)

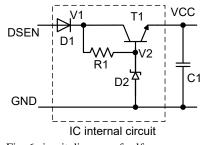

#### Self-Power Supply

When SR turns off, the voltage of DSEN will be pulled up. If the voltage of DSEN is higher than voltage of VCC, the charging current will flow to VCC from DSEN. As the DSEN exceed the Zener diode D2 breakdown voltage, the VCC will be clamped to the voltage. The charging current is limited to 30mA (typical value). If the voltage of DSEN is lower than voltage of VCC, the charging function is shut down. As in Fig. 6.

Fig. 6 circuit diagram of self-power supply

### UVLO

The IC leaves the under-voltage lockout state and activates the synchronous rectifier circuit when the voltage on the VCC pin is above  $V_{VCC_ON}$ . When the voltage drops below  $V_{VCC_OFF}$ , the under-voltage lockout state is entered and the SR driver output is actively kept low. As in Fig. 7.

Fig.7 circuit diagram of UVLO

### **Power design**

A few applications are shown as below. **Typical application specification**

| Products | Input range  | Output  | Temperature rise |

|----------|--------------|---------|------------------|

|          | 90Vac~264Vac | 12V/2A  | 53°C             |

| SY52257  | 90Vac~264Vac | 5V/2.1A | 51°C             |

The test is operated in natural cooling condition at 25 °C ambient temperature.

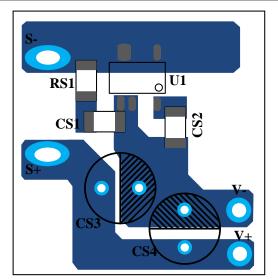

## Layout

(a) To achieve better EMI and Efficiency performance, the output connector should be connected to the output cap first, then to the SR Power pin.

(b) The circuit loop of all switching circuit should be kept small: secondary power loop, secondary RC snubber circuit loop and IC power supply loop.

Fig.8 layout example

### **Design Notice**

- 1. At no load, secondary side diode freewheeling time should be longer than 1.6us at no load.

- 2. To consider the reliability of SR switcher and the startup performance in all temperature range, the recommended value of VCC capacitance is 0.47uF.

- 3. To achieve better system ESD performance, the VCC cap should be close to SR switcher as soon as possible.

- 4. To achieve better EMI performance and improve the efficiency, the loop of secondary switching circuit should be kept as small as possible.

- 5. To prevent SR false turn on during SR off\_threshold adjustment stage, the primary switch should be turned on before second DCM resonant bottom.

- 6. To prevent primary and secondary switch conduct at the same time when circuit operates in Continuous Current Mode, the shut down time of primary switch should be larger than 24uS.

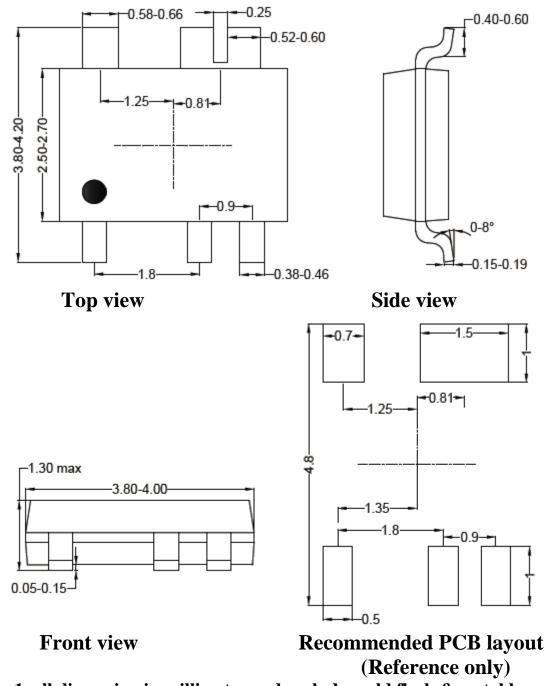

# **SOT335 Package Outline Drawing**

Notes: 1, all dimension in millimeter and exclude mold flash & metal burr; 2, the center line refers chip body center

## **Revision History**

The revision history provided is for informational purpose only and is believed to be accurate, however, not warranted. Please make sure that you have the latest revision.

| Date | Revision     | Change          |

|------|--------------|-----------------|

|      | Revision 0.9 | Initial Release |